- ALU 是计算机的运算器的重要组成部分,基本功能包括加减乘除四则运算和与或非异或等逻辑运算,以及移位、求补等操作。

一、加法器

- ALU 中的加法器是由全加器配以其他必要逻辑电路组成,根据全加器的个数加法器分为串行加法器和并行加法器。

1、一位全加器

- 全加器(FA)是基本的加法单元,电路结构如下图:

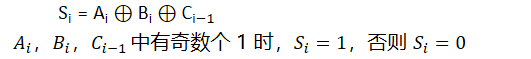

- Ai 和 Bi 是加数,Ci-1 是低位传进来的进位,这三个属于输入;Si 是本位和,Ci 是向高位的进位,这两个属于输出。全加器的逻辑表达式如下:

- 和表达式:

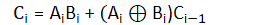

- 进位表达式:

2、串行加法器

- 若加法器中只有一个全加器,那么数据便要逐位送入加法器,这种加法器称之为串行加法器。对于串行加法器,操作数有多少位,就要进行多少次加法,每次产生一位和也同样是串行逐位送回寄存器,进位触发器用来寄存进位信号,以便参与下次运算。

- 串行加法器优点就是器件少、成本低;但是运算速度慢,因此用于对速度没有高要求的专用计算器。

3、并行加法器

- 若加法器中不止一个全加器,数据各位可以并行送入加法器进行运算,那么这种加法器称之为并行加法器。并行加法器的位数通常与机器的字长一样,可对数据的各位相加,但存在一个加法的最长运算时间问题,原因在于:虽然操作数的各位同时提供,但低位运算所产生的进位会影响高位的运算结果,例如:11…111 和 00…001 相加,最低位产生的进位将逐渐影响至最高位,因此并行加法器的最长运算时间主要由进位信号的传递时间决定,而每个全加器本身的求和延迟是次要因素。

- 因此,提高并行加法器速度的关键在于尽量加快仅为产生和传递的速度。

- 并行加法器的进位产生和传递如下:

- 并行加法器中的每个全加器都有一个从低位送来的进位输入和一个传递给高位的进位输出;通常将传递进位信号的逻辑线路连接起来构成的进位网络称为进位链。

3.1、串行进位

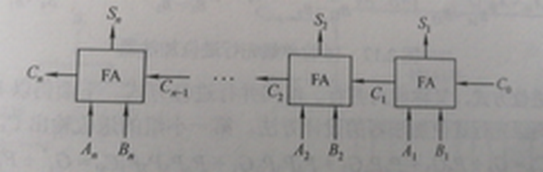

- 将 n 个全加器串联,从而达到进行 n 位数同时相加,此种逻辑电路组成的加法器称为串行进位的并行加法器,逻辑电路结构如下:

- 串行进位又称波形进位,每级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

3.2、并行进位

- 并行进位又称先行进位、同时进位,特点是各级进位信号同时形成。通常并行进位分为以下两种情况:

- 1)单级先行进位方式,又称为组内并行、组间串行进位方式;也就是将加法器的 n 个全加器分组。

- 2)多级先行进位方式,又称为组内并行、组间并行进位方式。

- 采用并行进位的方案可以加快进位产生和提高传递的速度。

二、ALU 结构

- ALU 是一种组合逻辑电路,典型 4 位 ALU 芯片(74181)的结构如下:

- ALU 的芯片也可以如同全加器构成加法器那样,由低位芯片采用一定逻辑电路组成多位 ALU。例如用 4 片 74181 芯片用串联组成 16 位 ALU,此时是一种片内并行、片间串行的结构,因为 74181 是一种 4 位并行加法器;也可以把 16 位 ALU 中的芯片分组,每 4 位一组,例如用 74181 与 74182(先行进位芯片)组合,组成一个 16 位两级先行进位 ALU,也就是片内并行、片间并行。