Vivado2018.3+Questa sim10.4e联合仿真新建工程及仿真基本流程

本文主要介绍了使用Vivado+Questa sim设计FPGA程序的基本流程,主要提供给刚学习FPGA的小伙伴们,希望能给大家带来帮助。

打开Vivado软件

双击打开Vivado软件

Create Project

单击Create Project 创建工程

点击Next

设置好Project name 和Project location 好后点击Next

选择RTL Project,点击Next,暂时不添加Sources和Constraints点击next跳过

选择芯片,这里使用的是xc7a100tfgg484-2,点击next

点击Finish,即完成对新工程的建立。

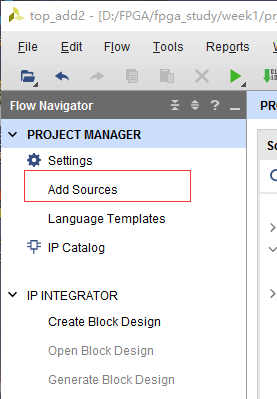

Add Sources

单击Add Sources

选择Add or create design sources,点击Next

如果自己写.v文件的话,点击Create File,如果调用以前的点击Add Files

输入File name,点击ok,点击Finish

点击OK,出现yes点击yes。

此时我们已经创建好了Sources,双击top_add2,进行代码的编写

这里使用最简单的一位加法器程序,下面给出代码

module top_add2(

input wire a,

input wire b,

output reg c

);

always @ (*) begin

c = a + b ;

end

endmodule

保存代码

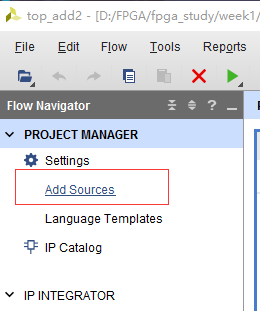

Create simulation soucrce

点击add Sources,选择Add or create simulation soucrce

点击Next

点击Create File,填写File name,点击OK,点击Finish,点击OK,步骤同上。等待updating后,对top_add2_tb进行编写

给出具体的代码

`timescale 1ns / 1ps

module top_add2_tb(

);

reg a=0;

reg b=0;

wire c;

top_add2 top_add2_inst(

.a(a),

.b(b),

.c(c)

);

initial begin

a=0;

b=0;

#100;

a=0;

b=1;

#100;

a=1;

b=1;

#100;

a=1;

b=0;

#1000;

$stop;

end

endmodule

Run Simulation

设置仿真器,点击Tools中的Settings

在Settings中找到Simulation,在Target Simulator 中选择Questa Advanced Simulator,点击Apply,点击OK

点击SIMULATION中RUN Simulation的Run Behavioral Simulation,

获得仿真结果

成功实现加法器的代码实现