一、时序检查

建立时间检查

建立时间指的是采样的D触发器在时钟上升沿之前数据需要稳定的时间。

reg-reg

数据在传输的过程中延迟值必须小于建立时间卡的那个时间点。

input to reg

creat_clock -name VIRTUALCLK -period 10 -waveform {0 5}

set_input_delay -clock VIRTUALCLK -max 2.55 [get_ports INA]

reg to output

set_output_delay -clock VIRTUALCLK -max 5.1 [get_ports ROUT]

set_load 0.02 [get_ports ROUT]

input to output

set_input_delay -clock VIRTUAL_CLKM -max 3.6 [get_ports INB]

set_output_delay -clock VIRTUAL_CLKM -max 5.8 [get_ports POUT]

保持时间检查

保持时间时钟上升沿之后数据依然要保持不变的时间。

reg to reg

input to reg

reg to output

input to output

多周期路径

正常情况下,两边的时钟是一样的,差了一个时钟周期T。但是有时候组合路径延迟值大于1个时钟周期。

creat_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFFO/Q] -to [get_pins UFF1/D]

上面这条指令时针对setup的。

如果在三个周期内完成组合逻辑,在第三时钟上升沿检查。

通常定好setup之后,hold在检查setup这个沿之前的一个时钟沿。

为了避免不合理的需求,需要对hold也要进行多周期约束。

set_multicycle_path 2 -hold -from [get_pins UFF0_Q] -to [get_pins UFF1/D]

这条约束就可以将检查hold的时钟沿向前推迟2个周期。

半周期路径

下降沿和上升沿。

对于时序路径是下降沿触发,上升沿接收。

通常来讲,A电路到B电路,想要更稳妥, 用半周期路径约束。半周期建立时间比较紧张,保持时间非常宽松。在数字电路中,setup如果违例比较容易好修正,但是hold如果违例比较难修。

伪路径set_flase_path

有些路径不可能发生,就叫做伪路径,告诉静态时序分析工具该路径不需要分析。通常发生在异步电路中。

set_flase_path可以指定某个时钟域到另一个时钟域,也可以指定一个pin出发,或者穿过一个pin。

san_clk扫描链时钟(DFT时候)

尽量少使用-through这个命令。

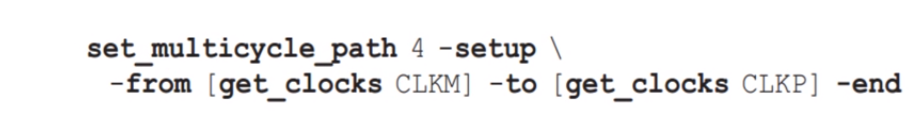

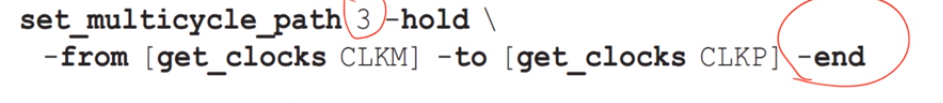

多时钟域的分析

慢时钟到快时钟

通常情况下,慢时钟域的数据并没有那么快,可以加个多时钟周期约束。

快时钟接受要加一个end

(这个部分有点懵)

对于慢时钟到快时钟,要给setup一个N的时候,也要给hold一个N-1。

start说明针对起始的快时钟进行约束。

上述这些分析都指的是同步时钟

多时钟