信号完整性的由来

一、逻辑波形和实际波形

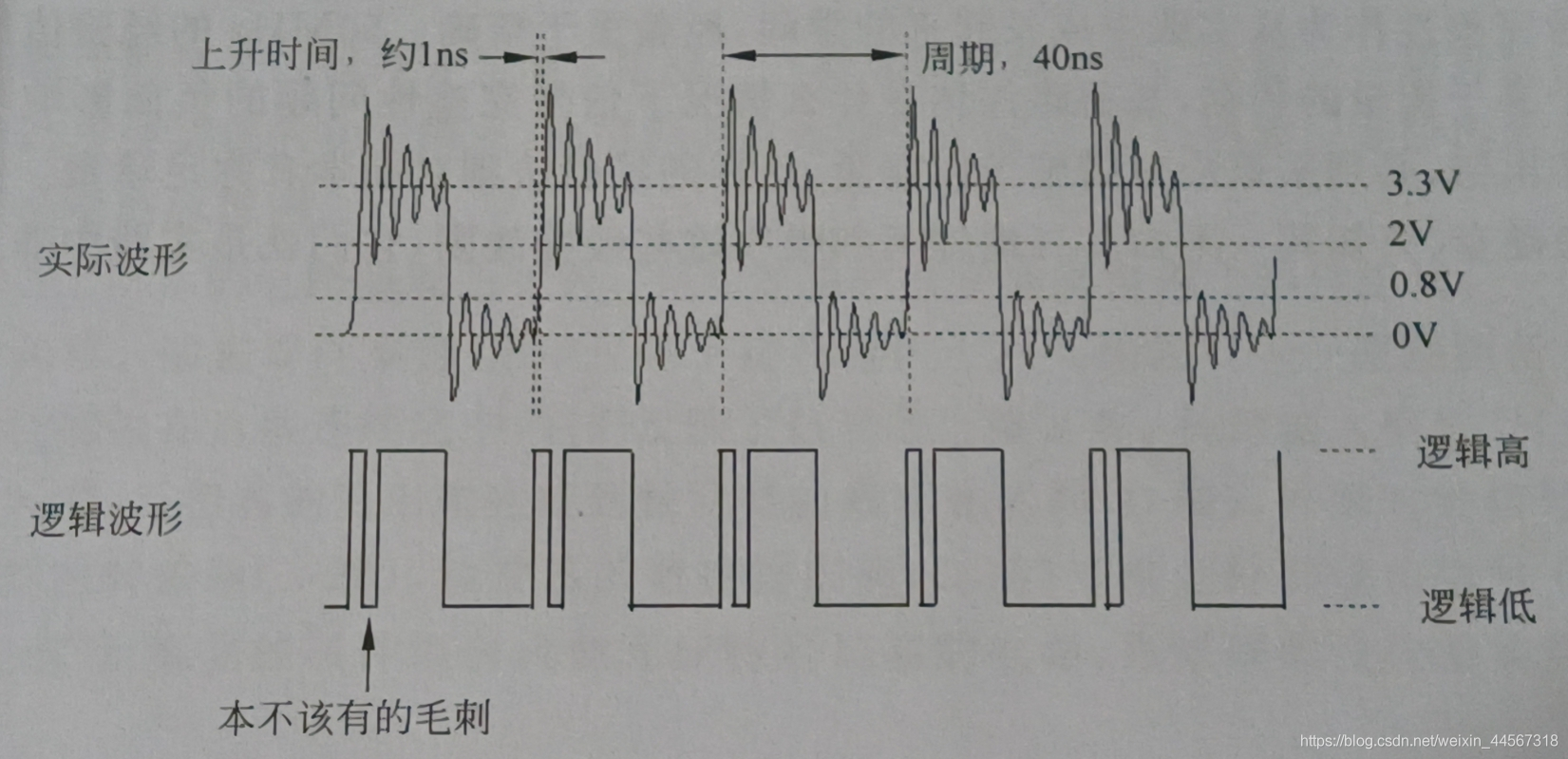

对于数字信号而言,完美的波形应该呈现出标准方波的波形。

然而,实际信号经由上升沿到达VCC和经由下降沿到达GND时,并不停止在VCC和GND上,而是继续向上、向下超出一小段幅度,而后经过几次“振荡”,才渐渐与VCC和GND吻合。

这些超出部分称为“过冲”和“下冲”。

造成信号波形“振荡”的原因是一种被称为“反射”的现象,这个现象在每个跳变的波形中都存在,只是引起的“振荡”幅度有大有小,对信号的危害也有轻有重。

二、电平标准与高、低点电平识别

二进制只有0和1两种状态,或称为高、低电平状态。

当信号波形电压高于某个特定的值(VIH)时,认为是逻辑高电平,当信号波形电压低于某个特定的值(VIL)时,认为是逻辑低电平。

不同的电平标准有着不同的VIH和VIL值。

在信号波形电压处于VIH和VIL之间时,被认作是高电平还是低电平,主要由集成电路芯片器件内部的构成机制和工作原理决定。

简单而言,数字电路芯片器件对于输入信号高、低逻辑电平的判定存在一个临界电压值,称为“阈值电压”。

三、信号完整性问题的产生

当“振荡”大到接收端芯片错误地识别信号的逻辑电平状态时,就会引起信号完整性问题。