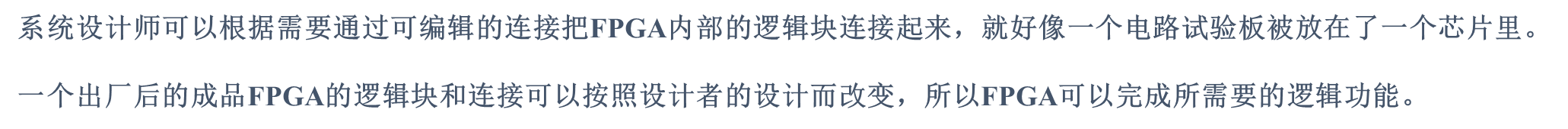

概述

verilog HDL

Verilog HDL基本结构

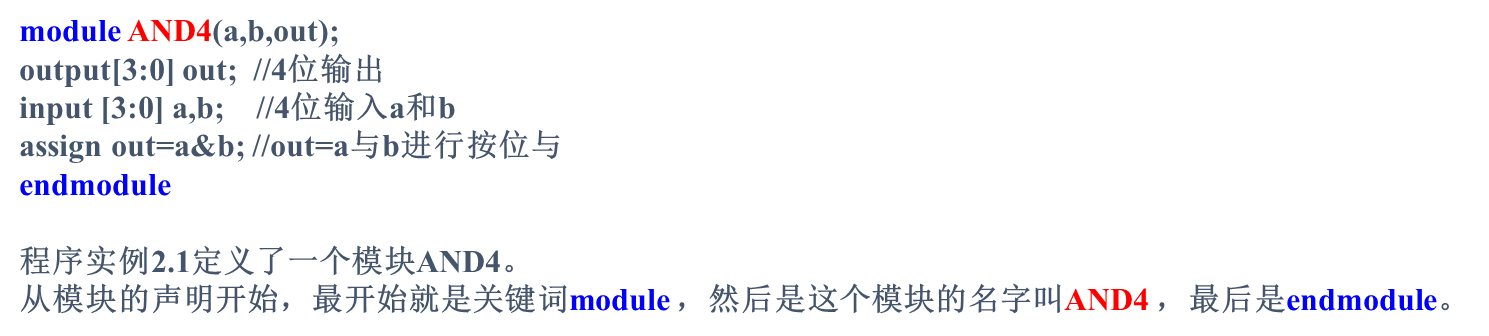

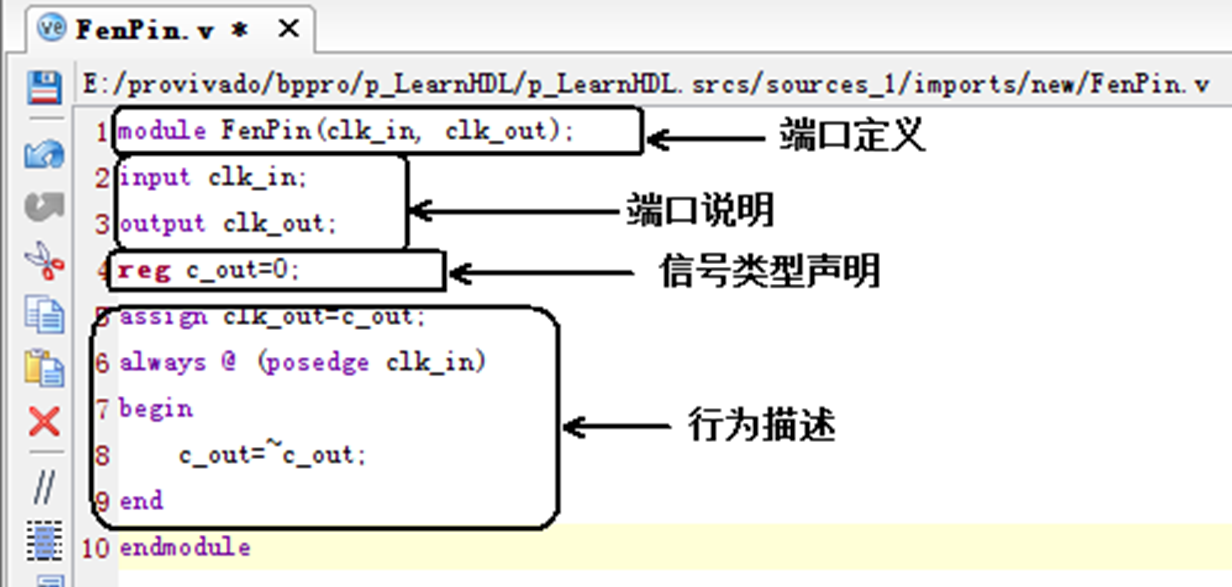

1 Verilog HDL程序是由模块构成的。每个模块嵌套在module和endmodule声明语句中。

2 每个Verilog HDL源文件中只有一个顶层模块,其他为子模块。可以每个模块写一个文件。

3 每个模块要进行端口定义,并说明输入输出端口,然后对模块的功能进行行为逻辑描述。

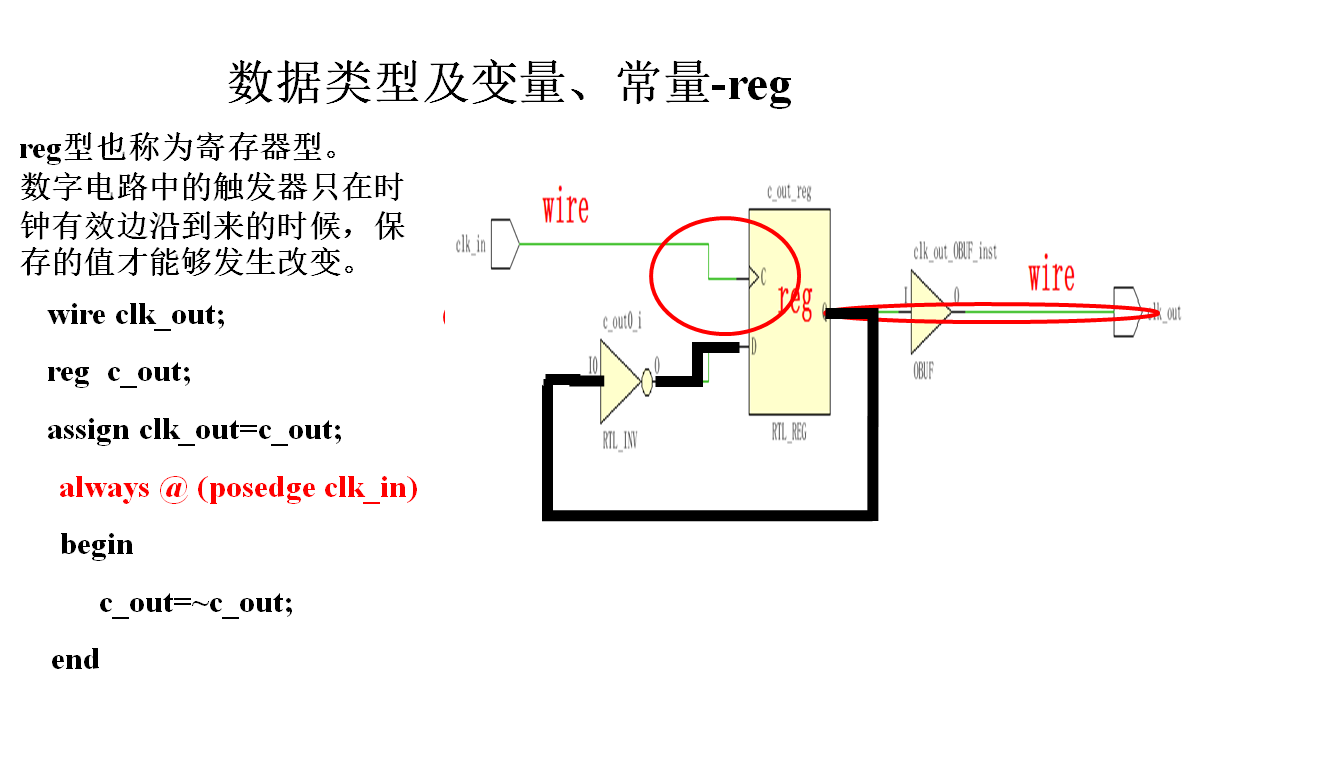

4 模块中的时序逻辑部分在always块的内部,在always块中只能对寄存器变量赋值。

5 模块中对端口或其他wire型变量的赋值,必须在always块的外部使用assign语句,通常是将寄存器的值送出。

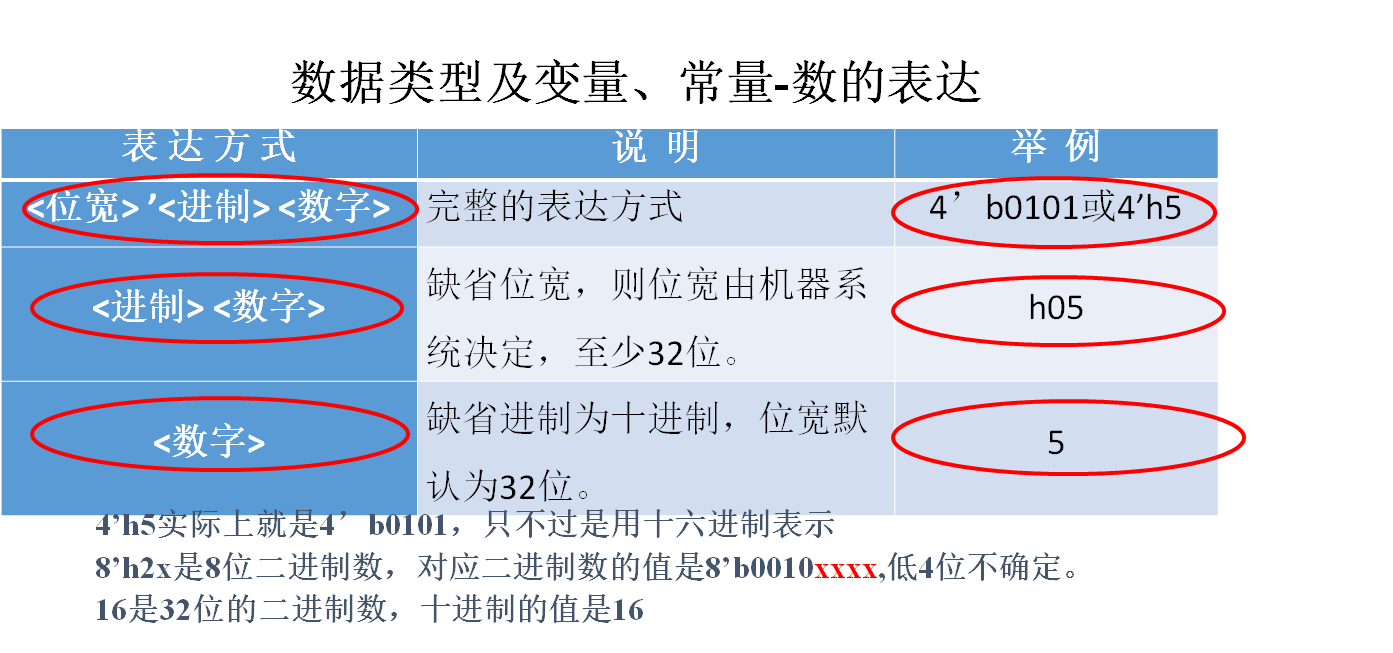

数据类型

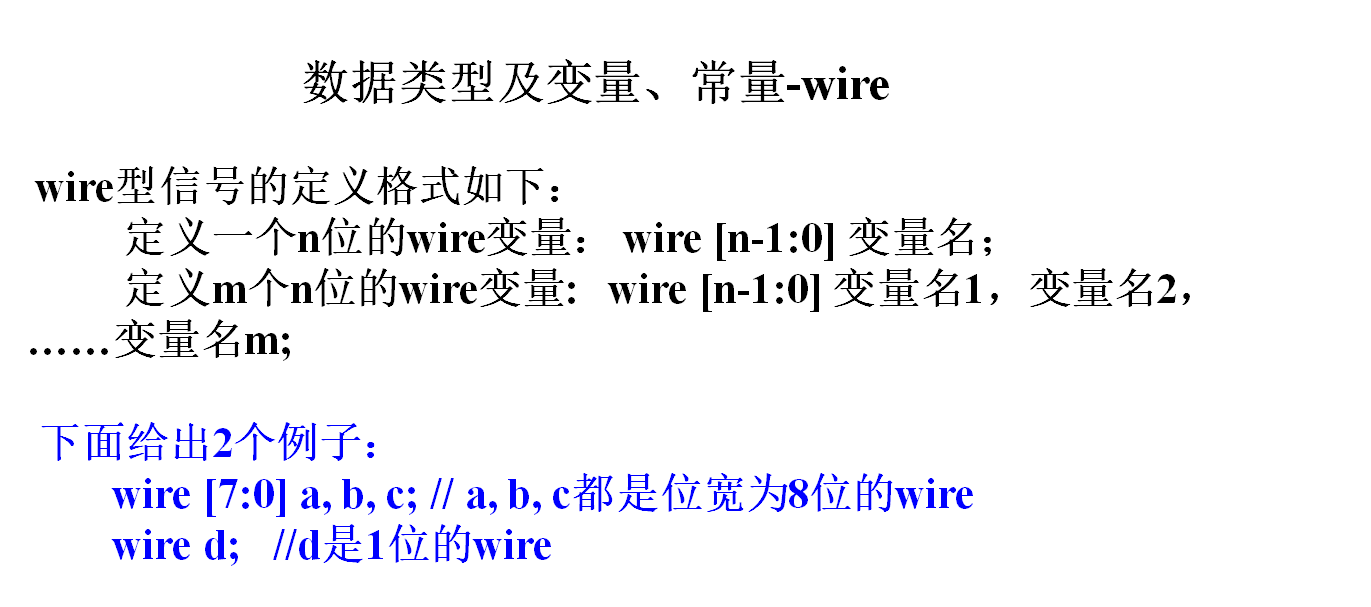

Verilog HDL有两种常用的数据类型,线网(Net)类型及变量类型。

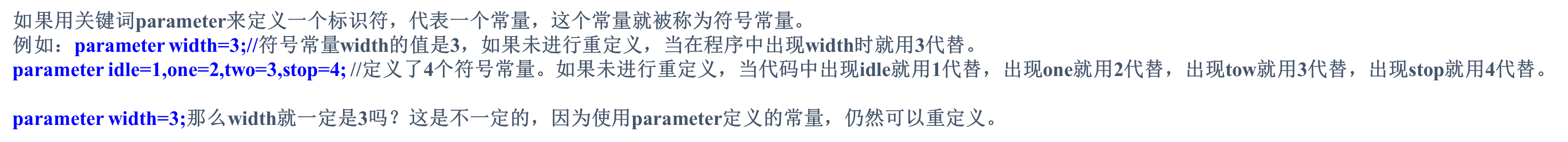

常量的值是不能够被改变的,变量的值是可以被改变的,例如寄存器型的变量reg。

从逻辑值和常量式开始,对于线网类型重点是常用的wire型变量,对于变量类型重点是reg型。

艹,不学了