版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/zyq_hh/article/details/53185894

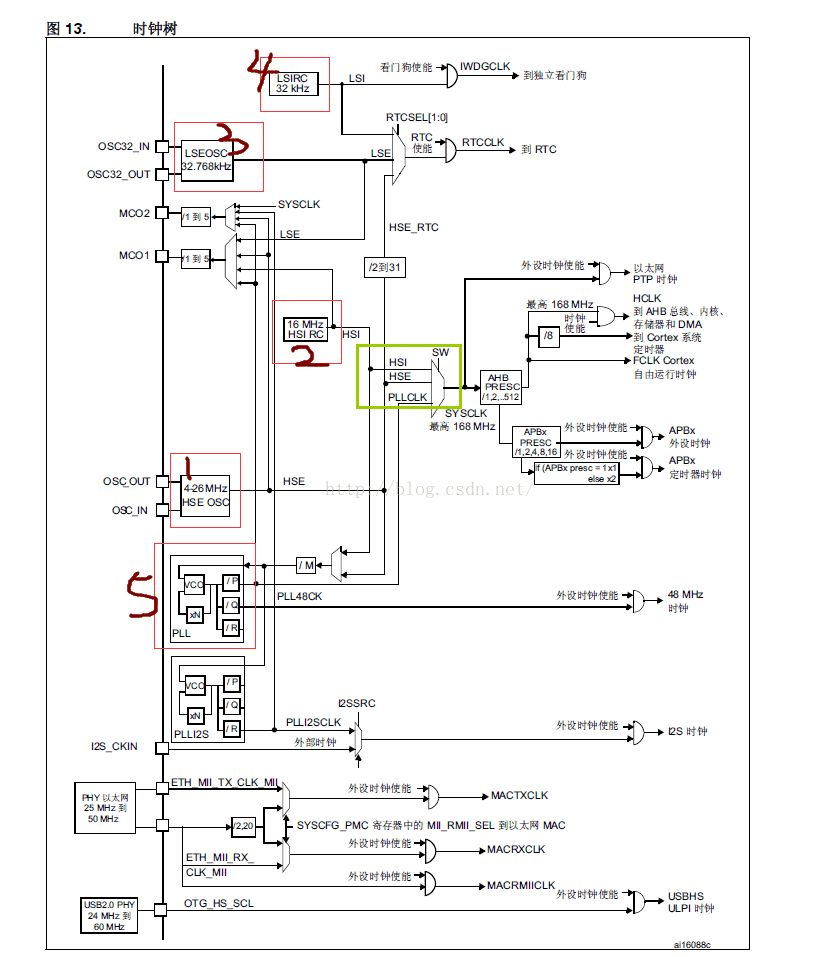

在我之前的文章中讲到了时钟的使能,我们通过查看系统的框架图,找到了AHB系统总线,在图中可以知道其为168MHz。那这168MHz是怎么来的呢,STM32中的时钟结构是怎样的呢?时钟的问题是一个很基础的问题,是学习一款单片机的核心,我们可以通过参考手册看看STM32的时钟树是怎样的。

在初始UART中我们使能了APB2,在上图中我们在左侧找到了APBx外设时钟,那么这个时钟源是怎么个回事呢?

stm32有5个时钟源分别是:高速内部时钟(HSI),低速内部时钟(LSI),高速外部时钟(HSE),低速内部时钟(LSE)和锁相环倍频输出(PLL)。

而我们的系统时钟能达到168MHz是怎么来的呢,根据上图,最大的HSE只达到了26MHz,所以我们使用的PLL来实现168MHz的。

在图里的第五块部分:

N表示倍频系数(取值范围:64~432),P表示系统时钟的主PLL分频系数(取值范围:2、4、6、8)

Q表示USB/SDIO/随机数产生器等主PLL分频系数(PLL之后的分频),取值范围:2~15。

R暂时用不上。

我们通常编写代码是会遇到

void Stm32_Clock_Init(u32 plln,u32 pllm,u32 pllp,u32 pllq)

Stm32_Clock_Init(336,8,2,7);//设置时钟168MHz;

外部晶振伟8MHz时,推荐使用N=336,M=8,P=2

得到Fvco =8*(336/8)=336MHz

Fsys=Fvco/2=168MHz

Fusb=Fvco/7=48MHz

通过SW选择SYSCLK=PLLCLK,即可得到168MHz的系统运行频率。继续通过分频就可得到相应的时钟频率了。