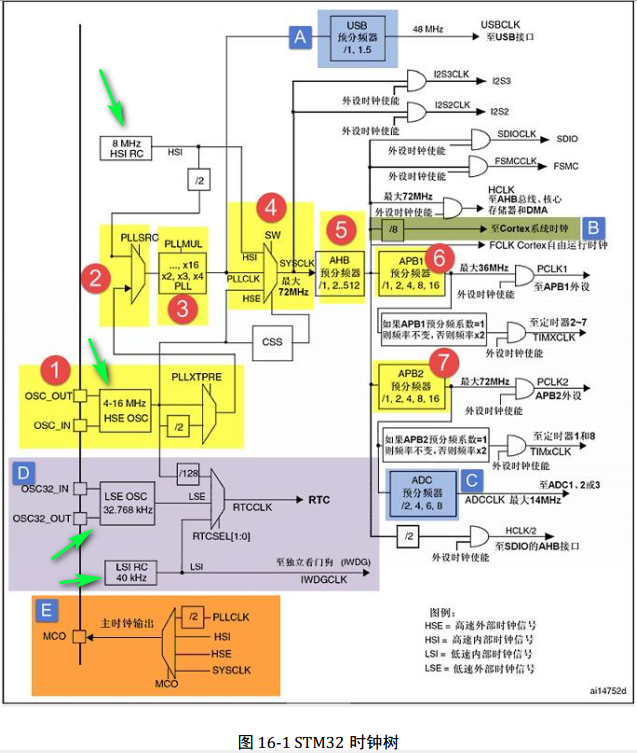

一、stm32时钟树

stm32时钟树:由时钟源到外设的结构框图。

基本时钟源(图中绿色箭头指出):

(1)HSI高速内部时钟,RC振荡器,8MHz。

(2)HSE高速外部时钟,石英/陶瓷谐振器,8MHz。

(3)LSI低速内部时钟,RC振荡器,40kHz。

(4)LSE低速外部时钟,RTC石英晶振,32.768kHz。

注:内部指的是片上外设,外部指的是芯片外部。

(5)除了上述基本时钟源,还有num3中的PLL锁相环倍频时钟源,它是将HSI和HSE倍频后输出。

二、PLLCLK - PLL时钟(num4)

时钟来源:(1)HSI/2 (2)HSE

三、SYSCLK - 系统时钟(num5)

时钟来源:(1)HSI (2)PLLCLK (3)HSE

SYSCLK经过分频后,得到AHB总线时钟HCLK;

HCLK再分频得到APB1总线时钟PCLK1和APB2总线时钟PCLK2;

PCLK2分频后得到ADCCLK最大14MHz。

四、RTCCLK(灰色框中)

时钟来源:(1)HSE/128 (2)LSE (3)LSI

五、系统时钟配置

系统时钟有三个来源,有三种配置方式。

7