版权声明:本博客内容来自于个人学习过程中的总结,参考了互联网、数据手册、帮助文档、书本以及论文等上的内容,仅供学习交流使用,如有侵权,请联系,我会重写!转载请注明地址! https://blog.csdn.net/Reborn_Lee/article/details/85949024

本文采用Vivado2014.4来完成一个二进制转格雷码的IP的设计与封装。

格雷码的编码原理:

实验步骤:

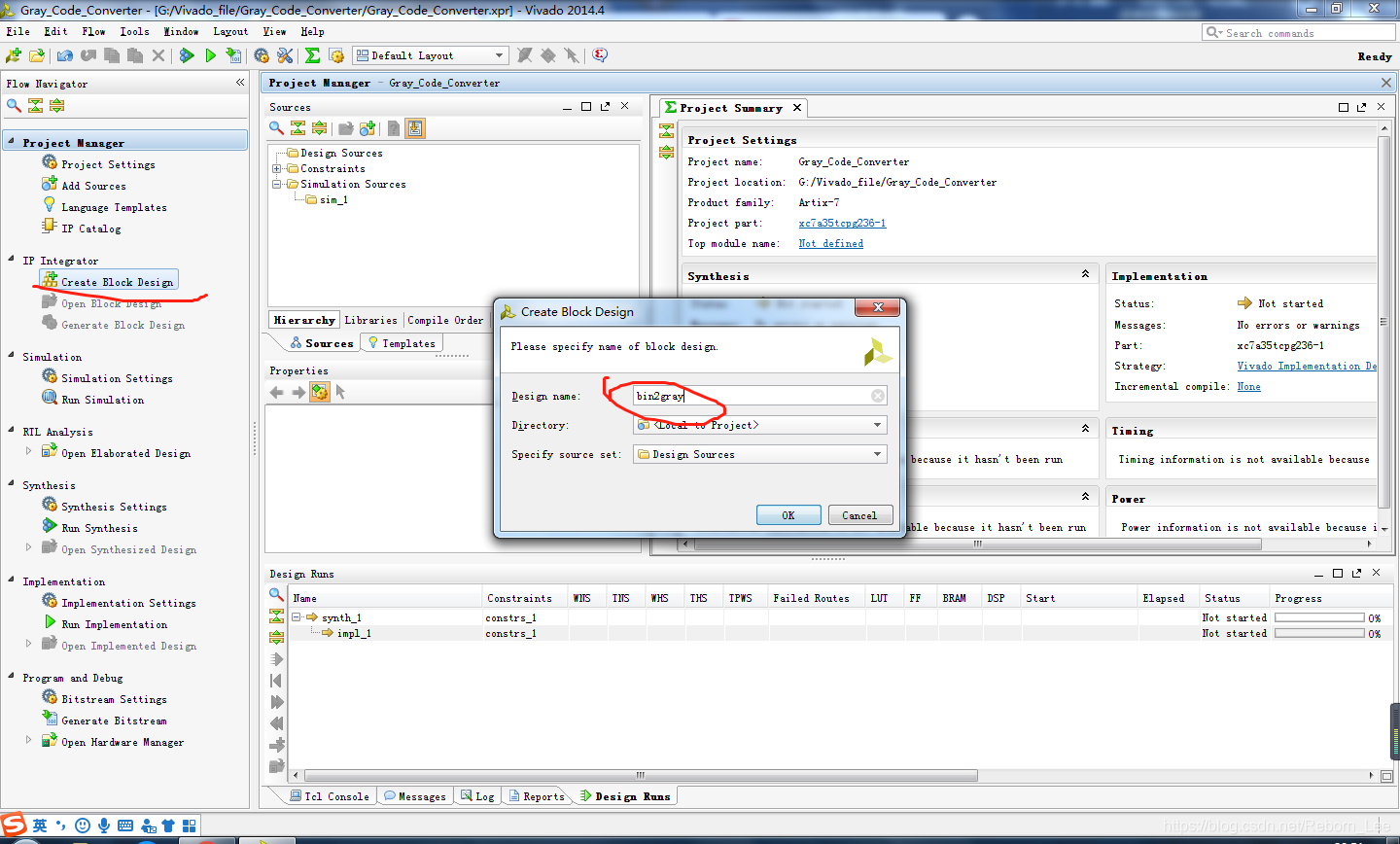

打开Vivado,创建名为Gray_Code_converter的工程,创建原理图,添加IP,进行原理图设计。

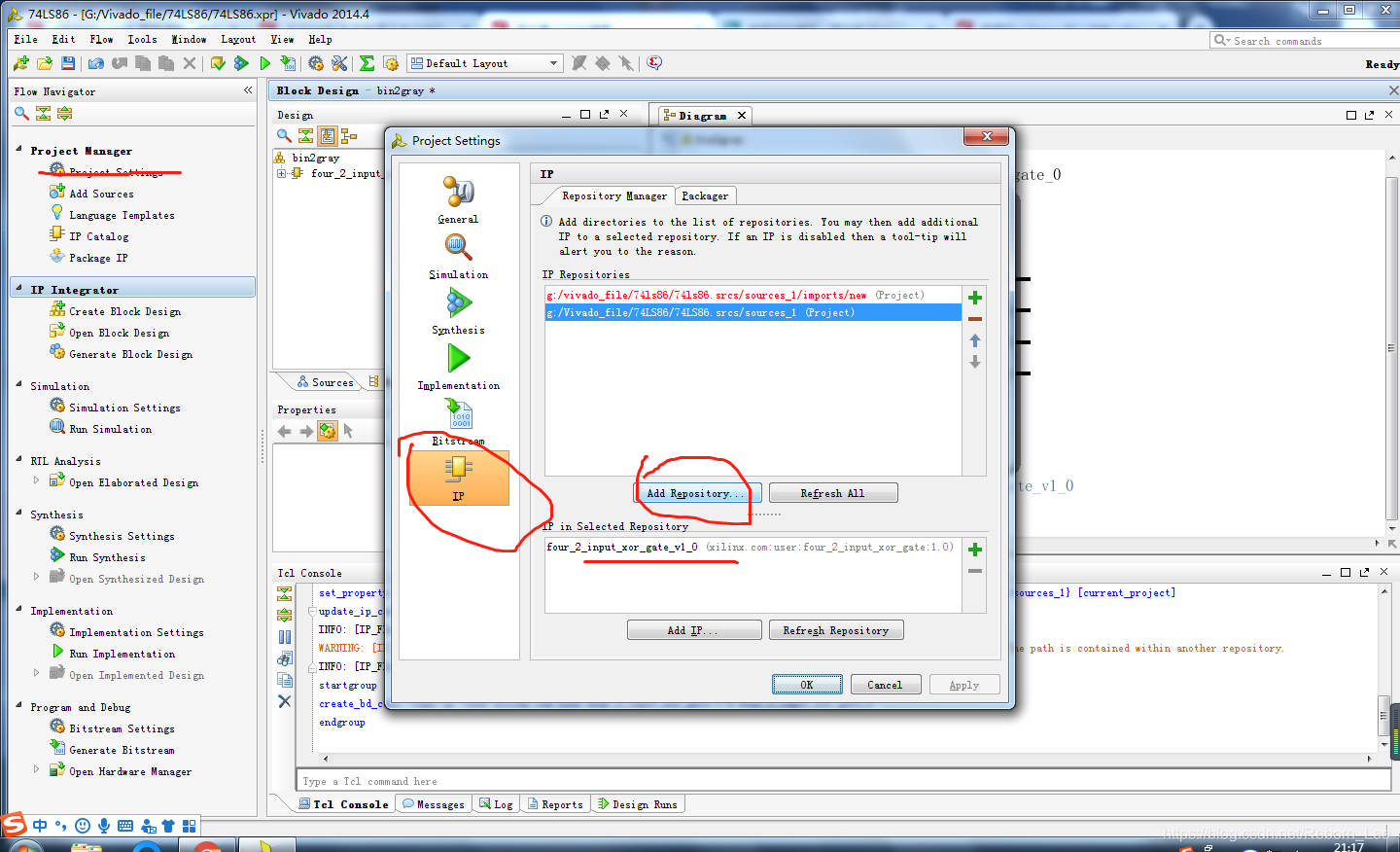

之前需要自己按照上篇博文的方式:打包属于自己的IP来创建一个2输入4位异或IP核。

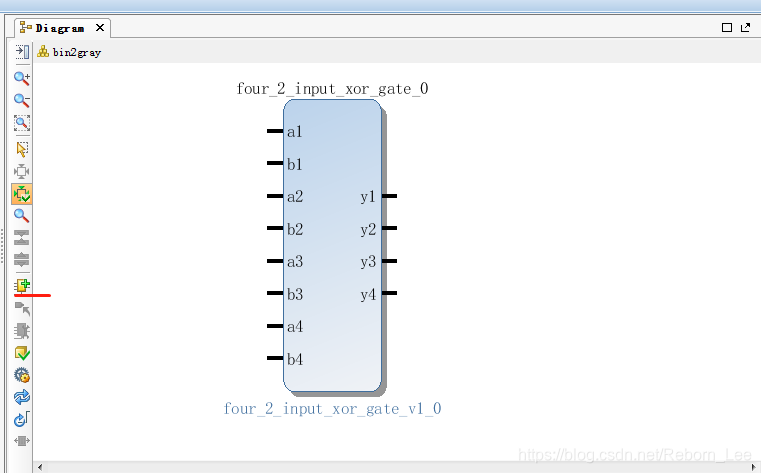

之后,通过下图方式将设计的IP添加进来:

右击端口,选择Make External来添加端口。

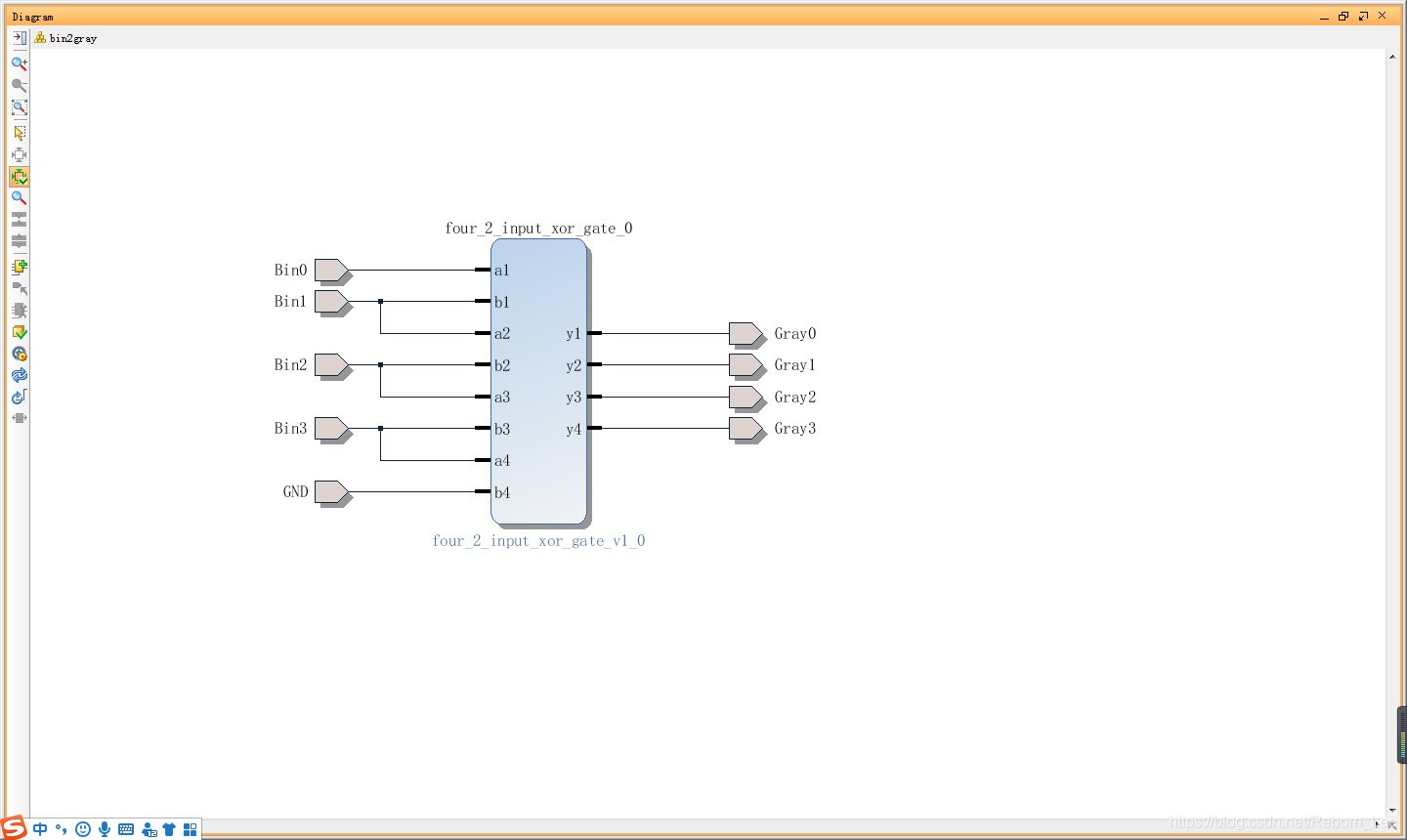

最终设计好的原理图如下:

在sources界面右击bin2gray,选择Generate Output Products,如下:

生成输出文件后,再次右击,选择Create HDL Wrapper,创建HDL代码文件:

至此,原理图已经完成。

之后的综合,实现和生成编译文件,不在话下。

例如,综合后的电路图: