两种模式基本设计实现

这里以Vivado自带的wavegen为例,通过用Tcl脚本的方式分别执行Non-Project模式和Project模式。这实现需要将RTL文件放在Src文件夹下,约束文件放在XDC文件夹下,而IP放置在IP文件夹下。

该工程的GUI操作参见:https://blog.csdn.net/qq_26652069/article/details/90613366

1.工程模式下的设计方式

该模式下的基本实现过程包括:创建新的工程、创建/添加设计文件、RTL描述与分析、设计的综合和分析过程、设计的行为仿真、创建实现约束、设计实现和分析、设计时序仿真、生成编程文件、下载比特流到FPGA开发板上。

1.1创建工程

(1)RTL Project:该选项表示通过Vivado集成开发工具管理从RTL创建到生成比特流的整个设计过程。在这个过程中设计人员可以添加:

- RTL源文件;

- Xilinx IPCatalog内的IP;

- 用于层次化模块的EDIF网表;

- Vivado IP集成器内创建的BlockDesgin;

- 数字信号处理(DSP)源文件。

其中IP可以包含以下类型:

- Vivado自己生成的XCI文件;

- 由Core Generator工具生成的已经过时的XCO文件;

- 预编译的EDIF或者GNC格式的IP网表。

设计人员利用集成开发环境可以进行RTL分析、启动和管理综合与实现的运行过程、分析设计的运行结果、尝试不同的约束和实现策略,达到时序收敛。

(2)Post-synthesis Project: 该选项允许设计人员使用综合后的网表来创建工程。设计人员可通过Vivado中集成的综合工具、XSt或第三方的综合工具综合得到的网表。例如在Vivado中可以导入EDIF、NGC结构的system Verilog 或结构化的Verilog格式的网表,以及Vivado设计检查点文件(DCP文件)。

设计者可以通过集成开发环境进行 逻辑网表的分析和仿真、启动管理不同的实现运行过程(没有综合了)、分析布局布线的结果、尝试不同的约束和实现策略。

(3)I/O Planning Project :该选项通过创建一个空的I/O规划工程,在设计的早期阶段就可以执行时钟资源和I/O的规划。开发人员可以在Vivado中定义I/O端口,也可以通过逗号分隔的值(CSV)或者XDC导入。

分配完IO后,Vivado工具可以创建CSV、XDC和RTL输出文件。当有可用的RTL源文件或者网表文件时,这些文件可用于设计的后期。

(4)Imported Project:该选项允许开发人员导入 原本由synplify、xst或者ISE设计套件所创建的RTL工程数据。通过该选项、将设计过渡到Vivado工具中。在导入这些文件时,同时也会导入工程的源文件和编译顺序,但是不导入实现的结果和工程的设置。详见:https://blog.csdn.net/qq_26652069/article/details/91902765

(5)Configure an Example Embedded Evaluation Board Design:从预定义的IP集成器模版设计创建 一个新的Vivado工程。

Tcl命令:

1.创建工程命令模板:(根据需要修改,默认是RTL工程)

create_project project_name/exampleDesigns/project_8 -part xc7vx485tffg1157-12.若想要.创建网表工程,按照下面模板输入命令

set_property design_mode GateLv1[current_fileset]3.可以输入下面的Tcl命令,在工程中添加设计源文件

add_files -norecurse -scan_for_includes ./designs/oneFlop.v4.通过一下命令将些文件放到当前工程的路径下

import_filles -norecurse ./oneFlop.v1.2创建并添加一个新的设计文件

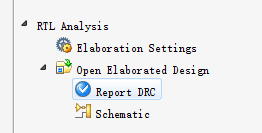

1.3RTL详细描述

可以打开原理图查看RTL级原理图,这是对HDL详细描述的网表结构。但是要注意的是,在此阶段中是不能推断出IO缓冲区的。

1.4设计综合和分析

综合就是将RTL级设计转换成门级描述,这个过程会进行逻辑上的优化,并且映射到Xilinx器件原语。

综合过程中,需要了解:

首先必须综合设计,但没有用于约束编辑器的书序约束;

当综合后,可以使用约束向导初步定义时序约束。

- 综合工具使用XDC文件约束驱动综合的优化,因此必须存在XDC文件;

- 时许约束上的考虑:

1.5行为级仿真

创建或添加仿真文件,进行仿真。

1.6 创建实现约束

实现约束的原理:综合后会生成综合网表,此时综合网表就可以与约束文件XDC或者Tcl脚本一起加载到存储器中,用于后续的实现过程。

1.6.1 IO规划器(I/O Planning)功能

可以通过I/O规划器实现约束引脚位置。器件的封装图提供了封装引脚、晶圆焊盘和I/O组,这样方便理解I/O组合逻辑之间的关系。

器件视图中,引脚之间的不同颜色区域标识了I/O组;同时显示 了差分对。

封装 引脚视图的功能表现在:

- 显示了I/O封装规范和分配的状态,允许设计这查看Trace延迟和引脚类型、典雅标准和差分对。;

- 在一个I/O组内,可以以一个组或列表的形式显示引脚。

- 拖拽时,图表显示引脚和I/O组布局状态。

可以在上面两幅中的任一个中分配I/O端口。

1.6.2 实现约束

(1)I/O Planning GUI操作实现

通过I/O planning图像界面进行端口配置。先创建约束文件**.xdc,综合完成后需要打开综合后设计后在下图中才会有“I/O Planning”选项,选择“I/O Planning”。

在I/O Ports窗口中,进行端口分配:在site标题下为信号分配FPGA上的引脚,并且在I/O Std标题下,为每个逻辑端口定义其I/O电气标准。

窗口中显示了工程中定义的所有端口,将总线分组到可扩展的文件夹,将端口显示为一组总线或列表形式以及图标标识I/O端口的方向和状态。

分配完FPGA引脚后,右击选择“Export I/O Ports”,在唐初的对话框中选中XDC,并将导出路径指向当前工程中之前建立好的**.xdc。点击OK完成,如此当打开这个xdc文件后,原本空白文档就会有对应的约束代码了。

(2) 通过文本输入设置实现约束

除了通过前面的图形化操作进行约束外,还可以直接在XDC文件中按照语法规则输入约束代码来对引脚进行约束。

I/O约束的语法有:

1)I/O引脚分配设置命令

set_property PACKAGE_PIN <pin_name>[get_ports <信号名>]2)I/O引脚的驱动能力设置命令

set_property DRIVE<2 4 6 8 12 16 24>[get_ports<信号名>]3)I/O引脚电气标准设置命令

set_property IOSTANDARD<IO电压标准>[get_ports<信号名>]4)I/O引脚抖动设置命令

set_property SLEW<SLOW|FAST>【get_ports<信号名>】5)I/O引脚上拉设置命令

set_property PULLUP true [get_ports <信号名>]6)I/O引脚下拉设置命令

set_property PLLDOWN true [get_ports<信号名>]其他I/O约束命令参考Xilinx官方手册。

1.7实现和分析

1.8时序仿真

1.9生成比特文件

1.10下载比特流文件到FPGA

2. 非工程模式基本设计实现

2.1基本命令和功能

(1)首先掌握非工程模式下的基本命令列表

| 命令 | 功能 |

| read_edif | 将EDIF或NGC网表导入当前工程的设计源文件集合中 |

| read_verilog | 读入用于非工程模式会话Verilog(.v)和System Verilog (.sv)源文件 |

| read_vhdl | 读入用于非工程模式会话的VHDL(.vhd或vhdl)源文件 |

| read_ip | 读入用于非工程模式会话的已经存在的IP(.xco或.xci)工程文件。使用来自.xco IP工程的.ngc网表。对于.xci IP,使用RTL用于编译;或者如果存在网表,则使用网表。 |

| read_xdc | 读入用于非工程模式会话的.sdc或者.xdc文件 |

| set_param set_property |

用于多个目的。例如,它可以定义设计配置、工具设置等 |

| link_design | 如果会话中使用网表文件,则对设计进行编译,用于综合目的 |

| synth_desgin | 启动Vivado综合,包含有设计顶层模块名字和目标器件参数。 |

| opt_desgin | 执行高层次设计优化 |

| power_opt_design | 执行智能时钟门控,用于降低系统的整体功耗(可选) |

| place_desgin | 对设计进行布局 |

| phys_opt_design | 执行物理逻辑优化,以改善时序和布线能力(可选) |

| route_design | 对设计进行布线 |

| report_* | 运行多个标准的报告,可以在设计过程中的任何一个阶段运行它 |

| write_bitstream | 生成一个比特流文件,并且运行DRC |

| write_checkpoint read_checkpoint |

在设计流程的任何点保存设计。一个设计检查点由网表和约束构成,它们在设计流程的该点进行了优化,以包含实现的结果 |

| start_gui stop_gui |

用于调用在存储器中当前设计的Vivado集成开发环境 |

(2)典型的Tcl脚本的使用

#将工作目录切换到指定目录下,设计的相关文件(属于输入文件)存放在该目录下

cd {F:\Vivado\file}

#define the output Directory area设置输出文件存放路径,比如生成的一些报告,日志,网表等文件

set outputDir ./wavegen_output

file mkdir $outputDir

#Set basic information

set top wave_gen

set part xc7k70tfbg676-1

#read IP files into in-memory

read_ip [glob -nocomplain ./ip/*.xcix]

#Read design files into in-memory

read_verilog [glob -nocomplain ./src/*.v*]

set_property FILE_TYPE "Verilog Header" [get_files clogb2.vh]

puts "Degin files reading successfully!"

#Read design constraints files into in-memory

read_xdc [glob -nocomplain ./xdc/*.xdc]

puts "Design files reading successfully!"

#Synthesis

synth_design -part $part -top $top

write_checkpoint -force $outputDir/${top}_synth.dcp

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_utilization -file $outputDir/post_synth_util.rpt

#opt 优化

opt_design -directive Explore

write_checkpoint -force $outputDir/${top}_opt.dcp

#place布局

place_design -directive Explore

write_checkpoint -force $outputDir/${top}_placed.dcp

report_utilization -file $outputDir/post_place_util_rpt

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

if{[get_property SLACK [get_timing_paths -max_paths 1 -nworst 1 -setup]] < 0} {

puts "Found setup timing violations => running physical optimization"

}

#Route 布线

route_design -directive Explore

write_checkpoint -force $outputDir/${top}_routed.dcp

report_route_status -file $outputDir/post_route_status.rpt

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_utilization -file $outputDir/post_route_util_rpt

report_drc -file $outputDir/pose_route_drc.rpt

#Bitgen 生成比特流

write_bitstream -force $outputDir/${top}.bit2.2

参考资料:

Xilinx 官方手册(Tcl或XDC相关的:ug894,ug895,ug903),《Vivado从此开始》、《Xilinx FPGA权威设计指南》(看中文版的话就买后面两本,看官方手册也可以)。