通讯总线

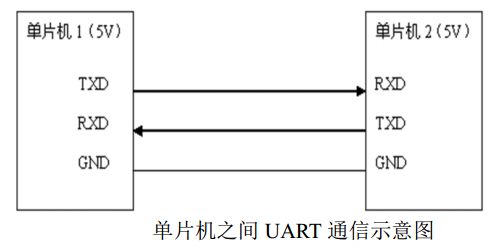

USART:

串行异步全双工

1. CD ← Carrier Detect 载波检测

2. RXD ← Receive Data 接收数据

3. TXD → Transmit Data 发送数据

4. DTR → Data Terminal Ready数据终端就绪

5. GND — System Ground 系统接地

6. DSR ← Data Set Ready 数据设备就绪

7. RTS → Request To Send 请求发送

8. CTS ← Clear To Send 允许发送

9. RI → 提示信号

协议:

数据包:

写: 起始位 + 数据位 + 校验位 + 停止位

读:

起始位:先发出一个逻辑0的信号,表示传输数据的开始 (0)

数据位:标准的数据位可以是5、7、8位,从最低位开始传输

校验位:奇偶校验和CRC校验

停止位:数据结束的标志,可以是1位、1.5位、2位的高电平

空闲位:处于逻辑1的状态,表示当前线路上无数据传输 (1)

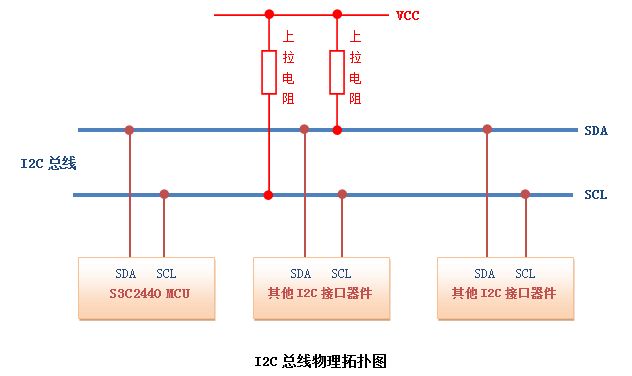

I2C:

串行同步半双工

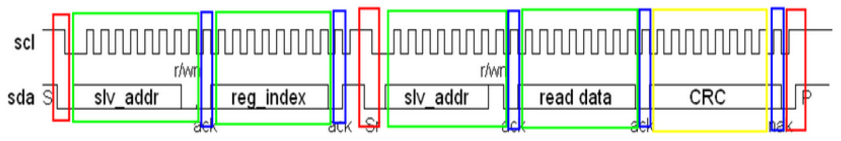

协议:

写:

读:

写: 起始—从机地址—应答—寄存器址—应答———发送数据—应答—校验信号—应答—停止

读: 起始=从机地址= 应答—寄存器址—应答———读取数据—应答—校验信号—应答—停止

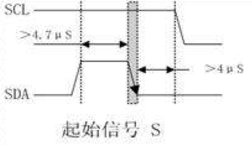

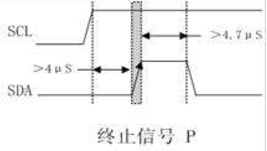

起始终止:

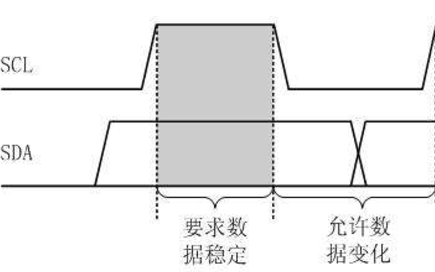

读取写入:

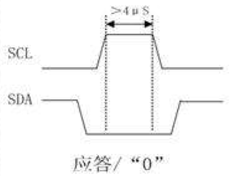

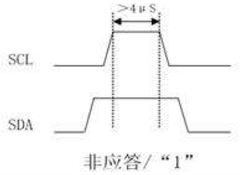

应答不答:

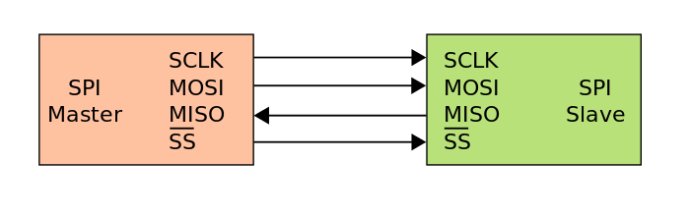

SPI:

串行同步全双工

协议:

SPI通信模式:

CPOL(时钟极性):0表示SCLK=0时处于空闲态,1则反之;

CPHA(时钟相位):0表示数据采样是在奇数边沿发送在偶数边沿,1则反之;

Mode0:CPOL=0,CPHA=0

(空闲时,SCLK为低电平,数据采样在奇数边沿:

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。)

Mode1:CPOL=0,CPHA=1

(空闲时,SCLK为低电平,数据发送在奇数边沿:

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。)

Mode2:CPOL=1,CPHA=0

(空闲时,SCLK为高电平,数据采集在奇数边沿:

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。)

Mode3:CPOL=1,CPHA=1

(空闲时,SCLK为高电平,数据发送在奇数边沿:

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。)

缺点:没有指定的流控制,没有应答机制确认是否接收到数据

CAN:

全称为“Controller Area Network”,即控制器局域网

协议:

I2S:

(Inter-IC Sound Bus)音频数据传输总线

协议:

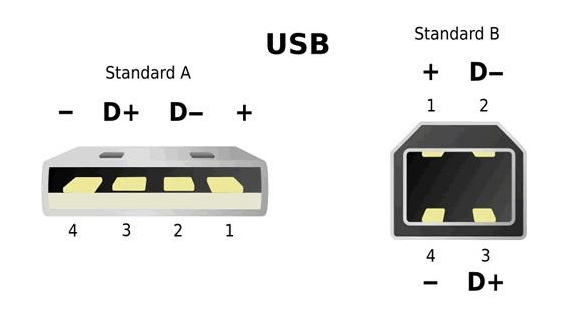

USB:

引脚1:电源(+5V)

引脚2:接入南桥,传输数据。

引脚3:传输数据。但两个引脚各有不同,是传输信息的高地位不同。

引脚4:地线

协议:

SDIO:

协议: