目录

微型计算机

理解微型计算机的工作原理才能更好的理解计算机、芯片、单片机等等的工作机理。本文从微机原理出发,整理相关知识并梳理,加深对计算机的理解。

基础电路

计算机由集成电路构成,可以说计算机是跑在芯片上的,芯片包括CPU芯片例如Intel生产的芯片,以及外设更多的单片机芯片如ARM等,后者是将CPU和一些存储器和外设集成在一个芯片上。所有的芯片均是由基本的门电路构成的,而门电路可以由硅单质掺杂形成的二极管和三级管构成,因此芯片通电后才能实现电平逻辑的变化。

上面大概梳理了一下不同器件的组成关系,可以看出芯片最终是由无数个门电路和相连的导线构成的,这也是为什么今天的芯片设计相关的视频介绍中往往以P型或N型半导体的构造为起点,由PN结构成的二极管和三极管组成的门电路是这个庞大工程的起点。

逻辑电路

逻辑电路是集成电路的最小单元,由3种基本门电路组成,

- 门电路

- 基本门电路

- 非门:$Y = \overline A \(,或门:\)Y=A+B\(,与门:\)Y=AB$

- 复杂逻辑电路(自行查找)

- 或非门,与非门,异或门,异或非门,异或同门,缓冲器(\(Y=A\),阻值变小)

- 基本门电路

- 门电路在芯片中的实现:

- 由硅单质经掺杂腐蚀等工艺形成P型半导体和N型半导体,两者相连部分叫PN结,PN结在正向电流时可导通,反向电流时阻断,具备单向导电性。在PN结上加入导线和封装,则构成一个二极管,由两个PN结构成一个三极管

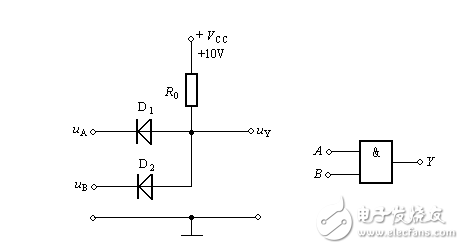

- 由于二极管的单向导电性,可以构成门电路(以与门为例):

基本运算与加法电路

- 半加器

- 两个二进制数(A和B)相加,最低位会产生两个结果,分别是和(S)和进位(C),能够实现一个二进制位加法运算的电路即半加器,半加器可以这样设计门电路(根据A、B相加后的运算结果):\(S=A \oplus B\),\(C=AB\)

- 全加器

- 将A、B、C一同运算产生S和新的进位C称之为全加器,全加器和半加器统称加法器,全加器相互串联即构成了二进制数的加法运算,常见的8位、16位、32位、64位为CPU的寄存器位数,不要混淆为加法器的个数(也和总线位数有关)。

- 现在一个CPU中含有的加法器个数非常巨大。

- 基本运算的实现(二进制):

- 减法:由加法计算A和B的补码即为减法

- 乘除法:由移位实现

基本组成电路

算数逻辑单元ALU

可进行加减法运算和逻辑运算的单元,计算机程序可以认为是程序和数据的组合,ALU即负责执行程序运算逻辑

触发器

- RS触发器,S指置位,R指复位,RS触发器可接一个时钟CLK用于运算同步,由于RS同时为低时会使输出无法确定,因此引入D触发器

- D触发器,D端为高,表现为S置位,D端为低表现为R复位,CLK在边沿变化时执行D触发器动作可以做到动作一致

- JK触发器是RS触发器的改进,相比RS触发器,在RS(JK)端同时为高时Q表现为反码,同时为低时Q表现为锁定,JK触发器可用用在计数器中。

JK触发器在JK均为低时

寄存器

- 一个触发器即一位寄存器,可知32位寄存器至少含有32个触发器

寄存器包括累加器,缓存器,计数器,可以知道用于缓存数据的寄存器由多个触发器连接而成,而每个触发器又是由多个门电路构成。

总线结构

三态输出电路:为了能够使用一组数据线(数据线条数取决于寄存器位数)便可以使任意两个寄存器相连

-

E A B 0 1 高阻 0 0 高阻 1 1 1 1 0 0 - E为控制,记L为装入门,L管理对寄存器装入数据,E管理由寄存器的输出。即在L打开时,寄存器可写入数据,而此时总线上的数据即被写入寄存器,当L关闭E打开时,总线上数据被寄存器更新。

-

根据寄存器位数可以得到总线的位数,同时还需要总线控制字CON确定数据的流向(从A寄存器到B寄存器还是从B寄存器到A寄存器),每次控制字中只有两位为高,其余均为低。

存储器

- 存储器可以认为是一大群寄存器构成的寄存器堆,根据使用的需要分为ROM和RAM,PROM可以认为是RAM和ROM的功能均支持。

- 数据线个数决定了每个地址有多少位数据可以取,地址线的个数决定了可以访问多少个地址。

基本工作原理

一个简化的微型计算机

该计算机实现一个简单的功能,计算A和B的加减法后停止。

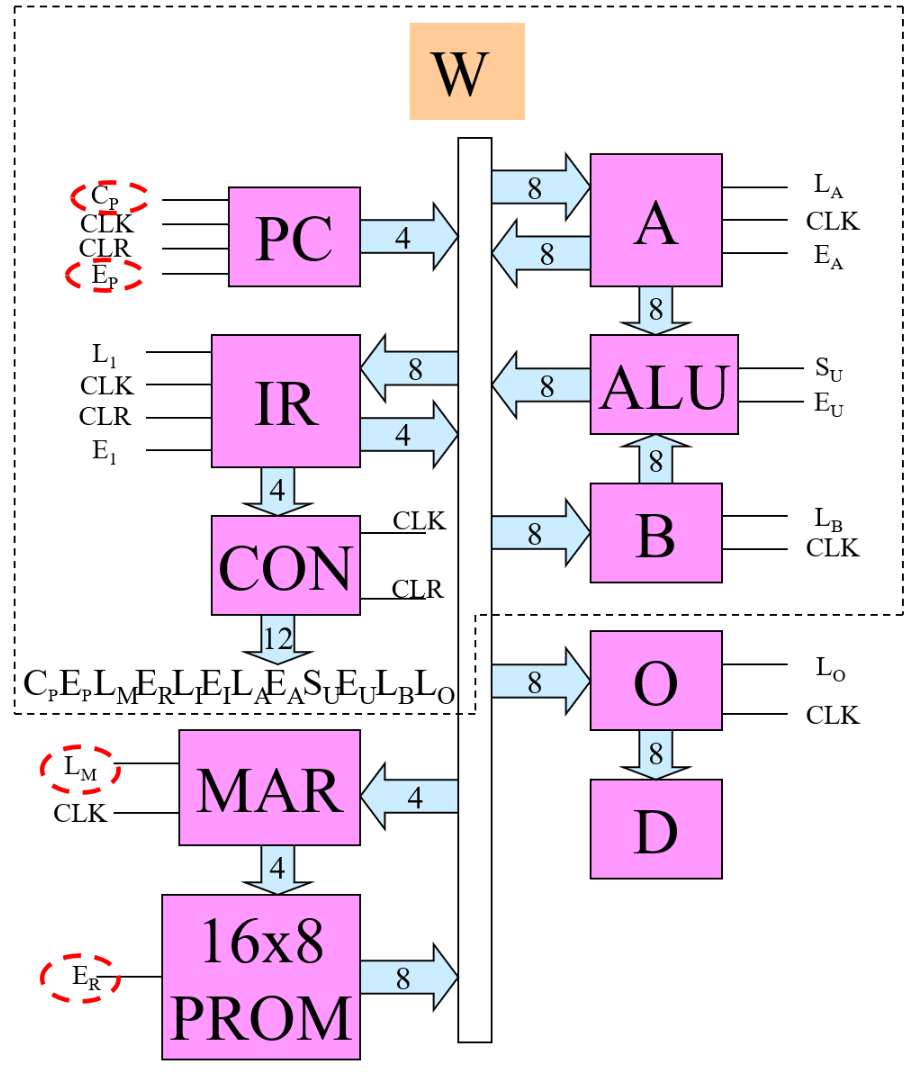

虚线框内可以认为是计算机的CPU,MAR和PROM构成存储器,O和D构成外设,将这些电路集成到一个芯片即为单片机。

PROM为8位,16个单元,即16个字节

CON总线控制字共12位,PROM存8位的指令字,经IR通过总线W取出后取高4位为指令,低4位为地址

指令系统与程序设计

- 假设支持5条指令,LDA:将数据送入累加器A,ADD:加法运算,SUB:减法运算,OUT输出,HLT停机

- 将指令与二进制操作码对应起来:LDA:0000,ADD:0001,SUB:0010,OUT:1110,HLT:1111

操作码的定义与xx有关

程序设计:

将PROM前8个字节给程序,后8个字节给数据,可知这个计算机只能执行8条指令以内的操作,操作的数据只有8个字节

假设执行的操作为(R9表示PROM第9个字节,RA等以此类推):

LDA R9 ADD RA ADD RB ADD RC SUB RD OUT HLT翻译为目的程序:

;PROGRAM:16+20+24+28-32 0000 1001 0001 1010 0001 1011 0001 1100 0010 1101 1110 0000 1111 0000 0000 0000 ;DATA 0001 0000;16 0001 0100;20 0001 1000;24 0001 1100;28 0010 0000;32 0000 0000 0000 0000 0000 0000注意,这里只是将汇编翻译为操作码

执行过程

假设环形计数器的位数是6位,则一个固定周期的CPU在可分为3个机器节拍的取指周期和3个节拍的执行周期,即一条指令的执行占用6个机器节拍,6个最小的时钟。不同的CPU在指令节拍个数上有所不同

- 取指周期:

- PC是程序计数器,这里计数范围为0-15,即0000-1111,上电复位时为0,PC被送入MAR时表示要取出的地址为0,即程序0000 1001,因此可以理解为程序从0地址开始执行。CON为011000000000

- 从MAR取出的指令被送入IR,将高4位解析给CON,低4位解析为地址,CON为000110000000

- PC加1,CON为100000000000

- 执行周期:

- 以LDA R9为例:LDA的操作码为0,设计逻辑门使CON送入0时执行以下动作:

- \(E_I=1\)将IR低4位送入总线,\(L_M=1\),MAR将总线的地址数据送给PROM,CON变为001001000000

- 将R9放入累加器A,CON变为000100100000

- 空拍,保持指令执行时间固定,CON为000000000000

- \(E_I=1\)将IR低4位送入总线,\(L_M=1\),MAR将总线的地址数据送给PROM,CON变为001001000000

- 以LDA R9为例:LDA的操作码为0,设计逻辑门使CON送入0时执行以下动作:

控制部件

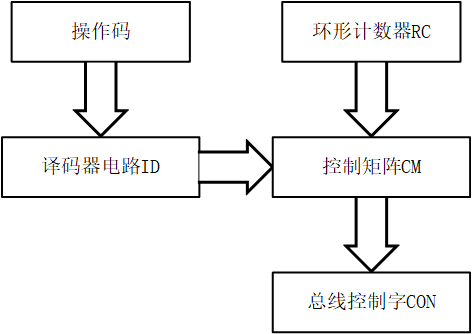

以LDA R9为例,LDA的操作码被定义为0000,而将0000翻译为CON的控制字的逻辑实现则需要指令译码器。译码器将操作码翻译为指令动作,在控制部件中,一个指令动作相当于一条信号线,假设一个CPU支持100条指令,则相当于操作码需要8位,输出100条信号线,再将这100条信号线与CON字映射起来:

这个过程中,操作码首先经过译码器电路翻译出执行的指令动作信号线,指令动作与一组CON控制字对应(上面的例子中LDA对应了3条CON),控制矩阵电路将RC和指令动作组合成一系列总线控制字,实现程序执行。

计算机的功能取决于CPU部分,而CPU部分取决于控制器的功能

其他技术

- 流水线技术:取指和执行可同时进行,采用流水线方式

- CACHE:高速缓存,CPU在访问存储器前先通过CACHE进行访问,如果指令存在则直接取走,不存在则访问存储器,提高了CPU访问存储器的速度

- 虚拟存储器:通过虚拟映射方式扩大可执行的范围,当程序大于RAM时可分批从存储器拷贝