2.1 可编程逻辑器件概述

FPGA是可编程逻辑器件(PLD)的一种,多种工艺,不同原理的PLD如下:

- PLA:可编程逻辑阵列

- PAL:可编程阵列逻辑

- GAL:通用阵列逻辑

- PROM:可编程只读存储器

- EPLD:可擦除可编程逻辑器件

- CPLD:复杂可编程逻辑器件

- FPGA:现场可编程门阵列

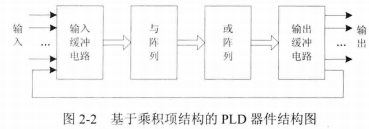

- 基于乘积项结构的PLD器件

- 原理上可实现任意的数字逻辑电路

- 绝大多数PLD都采用乘积项

- 多采用EEPROM或Flash工艺制作,掉电后不会丢失配置数据,器件规模一般小于5000门

- 基于查找表结构的PLD器件

- 规模易于做大

- 原理类似ROM

- 通过查找表实现函数功能,函数值放在SRAM,其地址线即输入变量,不同输入通过MUX找到对应函数值并输出

- 绝大多数FPGA器件都是基于SRAM结构实现,特点是集成度高,逻辑功能强,可实现带膜的数字系统设计和复杂的算术运算

- 缺点是掉电后会丢失配置数据,需外挂非易失配置器件以存储配置数据。

2.2 基于PLD的数字系统设计流程

2.2.1 设计输入

- 原理图输入

- HDL文本(HDL硬件描述语言)

2.2.2 综合

将原理图或者HDL转化为逻辑电源组成的电路网表

2.2.3 布局布线

- 将电路网络映射到具体的目标PLD器件,并产生可下载文件的过程

- 布局布线后产生如下重要文件:

- 芯片资源耗用情况报告

- 产生延时网表结构,以便于进行精确的时序仿真

- 器件编程文件

2.2.4 下载

对CPLD器件的下载称为编程,对FPGA器件的下载称为配置

2.2.5 仿真

包括功能仿真和时序仿真

2.2.6 工具介绍

此书设计实现OpenMIPS处理器时使用工具如下:

- 设计输入工具:UltraEdit

- 仿真工具:ModelSim

- 集成工具:Quartus II

2.3 Verilog HDL简介

- 书籍推荐《数字系统设计与Verilog HDL》

2.4 Verilog HDL中模块的结构

- 模块声明

- 端口定义

- 数据类型说明

- 逻辑功能描述:assin,always,例化

2.5 Verilog HDL基本要素

2.5.1 常量

常量有三种:整数,实数,字符串

2.5.2 变量声明与数据类型

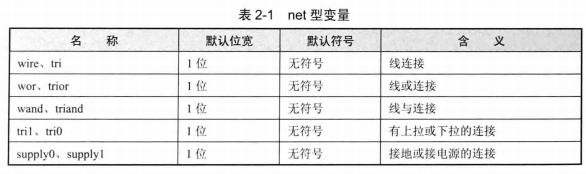

1.net型变量

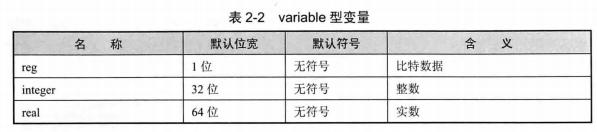

2. variable型变量

2.5.3 向量

变量位宽大于1为向量

2.5.4 运算符

算术、逻辑、位、关系、等式、缩位移位、条件运算符等

2.6 Verilog HDL行为语句

2.6.1 过程语句

- always过程语句

- initial过程语句

2.6.2 赋值语句

- 持续赋值语句:assign

- 过程赋值语句:阻塞与非阻塞赋值

2.6.3 条件语句

- if-else

- case

2.6.4循环语句

- for

- forever:用于testbench产生周期性波形

- repeat

- while

2.6.5 编译指示语句

- 宏替换 `define

- `include语句

- 条件编译语句:

ifdef,else, `endif

2.6.6 行为语句的可综合性

2.7 电路设计举例

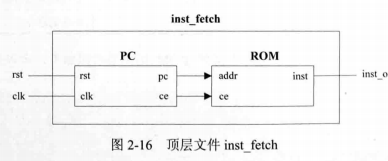

一个简化的取指令电路:PC模块,指令存储器

- PC模块的设计与实现

- 指令存储器ROM的设计与实现

- 顶层文件

2.8 仿真

2.8.1 系统函数

存储器两种初始化方法,一种是对存储器中诶个存储单元依次给初值,另一种是使用系统函数$readmemh

2.8.2 Test Bench

给激励,观察响应

2.8.3 ModelSim仿真

- 建立ModelSim工程

- 开始仿真