概述

Xilinx DDS主要用于产生正弦信号,在无线通信上下变频中使用的比较多,下面将阅读DDS IP手册的理解及实际工程(SIN/COS LUT模式)使用过程作如下总结。

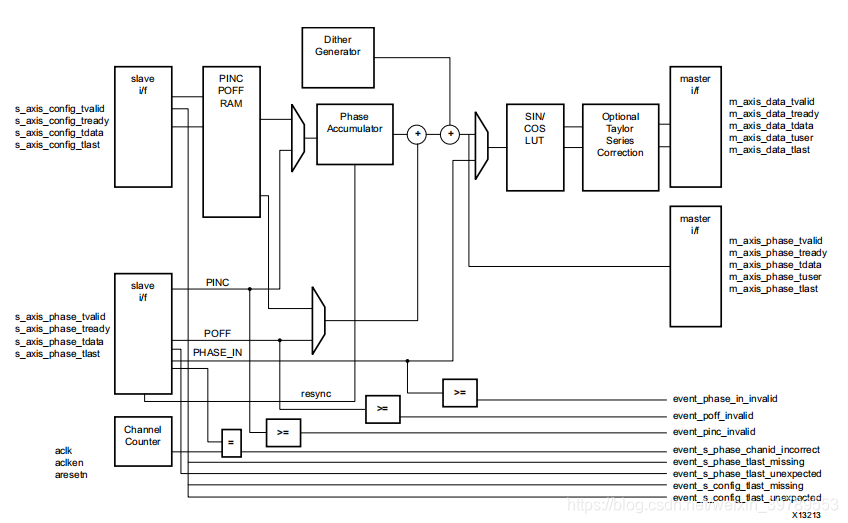

DDS内部组成

DDS内部主要由相位产生器(Phase Generator)和查找表(SIN/COS LUT)这两部分组成,这两部分可以独立使用,也可以合并使用,因此在实际使用中可以配置成三种模式:Phase Generator、SIN/COS LUT、Phase Generator+SIN/COS LUT。DDS的内部组成如下图所示。

DDS关键参数计算

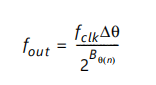

1、正弦信号频率

DDS产生的信号频率fout的计算公式如下,其中fclk为系统工作参考时钟频率,也可以该信号的采样频率fs,deta为相位增量对应的bit值,分母表示用多少位bit对应的2pi。例如信号采用率120Msps,每次相位增量对应的值为12(注意这里是十进制的12),相位用10bit表示,则产生的信号频率fout=(120×10^6*12) / (2^10)=1.406250 MHz。也可以这样理解这个公式:正弦波一个周期内采用的点数为fs/fout,等于2pi映射对应的数字除以相位增量对应的数字。

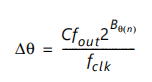

(公式1)

(公式1)

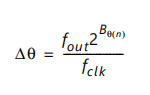

2、相位增量数值

根据上面正弦信号频率公式,可以推导出相位增量数值为:

(公式2)

(公式2)

当用于产生C路通道信号时,相位增量数值为:

(公式3)

(公式3)

3、频率分辨率

这里的频率分辨率可以暂且理解所能表示的最小频率,还是公式1所示,当相位增量deta为1,即为最小时,所能表示的最小频率即为频率分辨率。

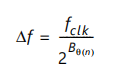

(公式4)

(公式4)

4、Rasterized(栅格化)模式

注意在选择Rasterized(栅格化)模式时,分母需要替换,信号频率、相位增量、分辨率公式均有变化,例如信号频率变为:

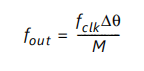

(公式5)

(公式5)

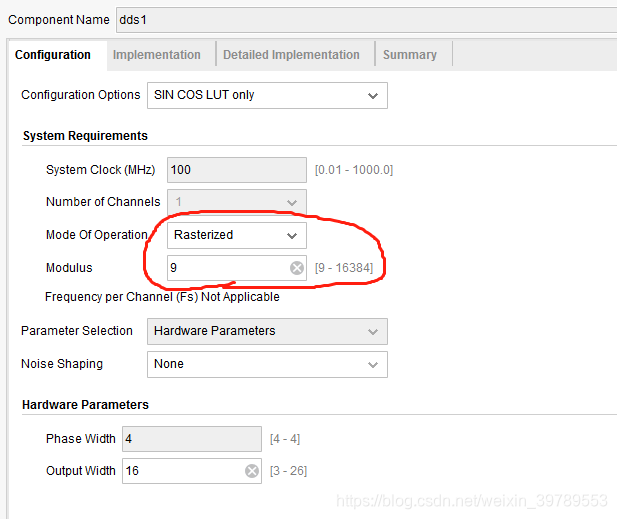

Rasterized(栅格化)模式配置界面参见下图

实际工程说明

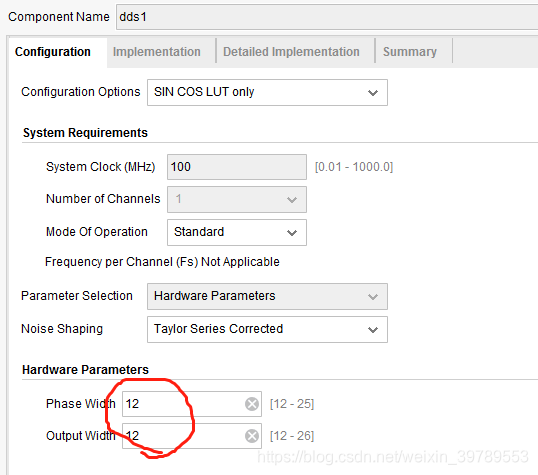

在实际工程中我们选择了SIN/COS LUT模式,因此相位增量通过AXI接口由主控写道FPGA寄存器phase,使能信号需要自行产生,输入相位增量为16位,输出的正弦信号SIN和COS各16位,代码参见如下:

//DDS

reg phase_en1;

reg [1:0] cnt1;

reg [11:0] phase1;

always @ (posedge data_clk or negedge start)

if(!start)

begin

cnt1<=2'd0;

phase1<=12'd0;phase_en1<=1'b0;

end

else

begin

cnt1<=cnt1+1'b1;

if(cnt1==2'd0)

begin phase_en<=1'b1;phase1<=phase1+phase;end

else phase_en<=1'b0;

end

wire [31:0] m_tdata;

dds1 dds1 (

.aclk (data_clk ),// input wire aclk

.s_axis_phase_tvalid (phase_en ),// input wire s_axis_phase_tvalid

.s_axis_phase_tdata (phase1 ),// input wire [15 : 0] s_axis_phase_tdata

.m_axis_data_tvalid (dds_en ),// output wire m_axis_data_tvalid

.m_axis_data_tdata (m_tdata ) // output wire [31 : 0] m_axis_data_tdata

);

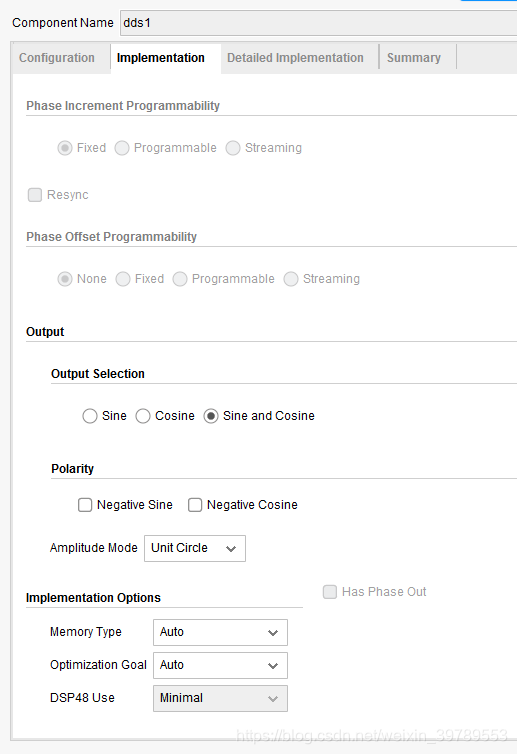

配置界面如下,注意配置界面中相位及信号位宽与实际例化的不一致。

注意配置界面中无输出有效信号,与实际例化的也不一致。