数字IC设计——跨时钟域篇2(亚稳态)

一、建立时间与保持时间

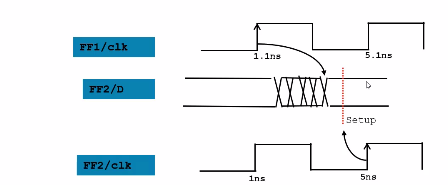

前提条件:对任何一种触发器,在时钟触发沿前、后的一个小时间窗口内,输入信号必须稳定。

输入信号应提前时钟上升沿 (假设上升沿有效)T时间到达芯片,这个T就是建立时间Setup time。

保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。

二、亚稳态

-

亚稳态

触发器无法在某个规定的时间段内,达到一个可确认的状态。亚稳态会带来功能的错误。

当发生亚稳态时,既无法预测该单元的输出电平,也无法预测何时才能稳定在某个正确的电平上。

-

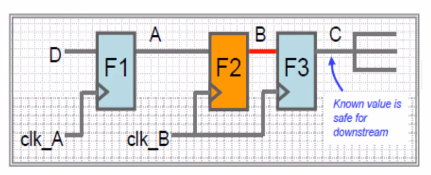

亚稳态传播

这种无用的输出电平可以沿信号通道上的各个触发器级联的方式传播下去。

三、如何处理亚稳态

-

如何处理亚稳态?

1.降低系统时钟(基于建立时间,适当降低系统频率来满足时序约束)2.用反应更快的FF

3.引入同步机制,防止亚稳态传播

4.改善时钟质量,用边沿变化快速的时钟信号

扫描二维码关注公众号,回复: 14266958 查看本文章

-

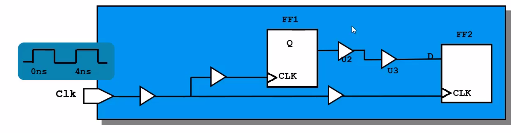

二级寄存器

使用同步器降低亚稳态发生的概率

1.亚稳态需要一段时间才能到达稳态

2.二级寄存器可以增加一个clock cycle的时间使亚稳态稳定

-

MTBF

MTBF—Mean Time Between Failure

平均故障间隔时间

两级同步并不能完全隔离亚稳态危害,但极大降低了亚稳态发生概率。\

使用同步器降低亚稳态发生概率

- 对于二级触发器,480MHz的频率比1000MHz频率的寿命要长很多;

- 对于1000MHZ,三级触发器要比二级触发器寿命长

设计时可以参考上表,如果设计的时钟频率比较高,建议采用三级触发器同步的方式。

四、亚稳态常见问题

1. 亚稳态的二级处理(增加一个clock cycle的时间)

- 亚稳态是指信号跳变时,由于不满足建立保持时间,寄存器的输出端会输出中间电平,或者产生震荡等。亚稳态不是一个持续的状态,是一个短暂的状态。

- 对于异步信号,一级寄存器永远会有亚稳态的可能。

- 如果第一级寄存器出现亚稳态,亚稳态的时间如果在1个clock cycle之内恢复了,那么第二级寄存器会采样到稳定状态。如果亚稳态时间过于长超过1个clock cycle,那么第二级仍然有可能输出亚稳态。

- 亚稳态不是纠错,如果产生亚稳态,那么采样值可能是不正确的,两级寄存器或者多级寄存器的级联是防止亚稳态状态在时序电路中传播扩散。

2. 增加寄存器避免亚稳态,但这能保证输出逻辑是正确的么?

增加寄存器可以避免亚稳态传播,但是不能纠正逻辑正确性。

多级寄存器可以保证最后一级能够采样到稳定的值。但不一定能够采样到正确值。