因为我的工程比较大,综合时间有点长,之后在上面做图像处理算法的实现,然后发现加上这个模块之后综合的时间特别就,达到了3个小时,查阅了好多资料也不知道怎么去解决这个问题,今天听一位高人指点,终于解决了这个问题,于是就想把这个解决方案记录下来。

首先说明一下我的工程环境,我用的是Quartus II 64-Bit Version 15.0.2 Build 153 07/15/2015 SJ Full Version。

其实这个问题很容易解决,就是在Assignments->Settings…->Compiler Settings…->Prevent register merging这个选项勾选上,即阻止这个优化就可以了。

问题是解决了,可是这个选项什么意思呢。知其然也要知其所以然,对吧。首先说一下这个设置的中文翻译,也就是阻止寄存器融合,具体是干什么的呢,网上的资料也不是很多,我先把官方的一些解释贴出来。

首先是Altera 15.0 Help 中关于Disable Register Merging的解释

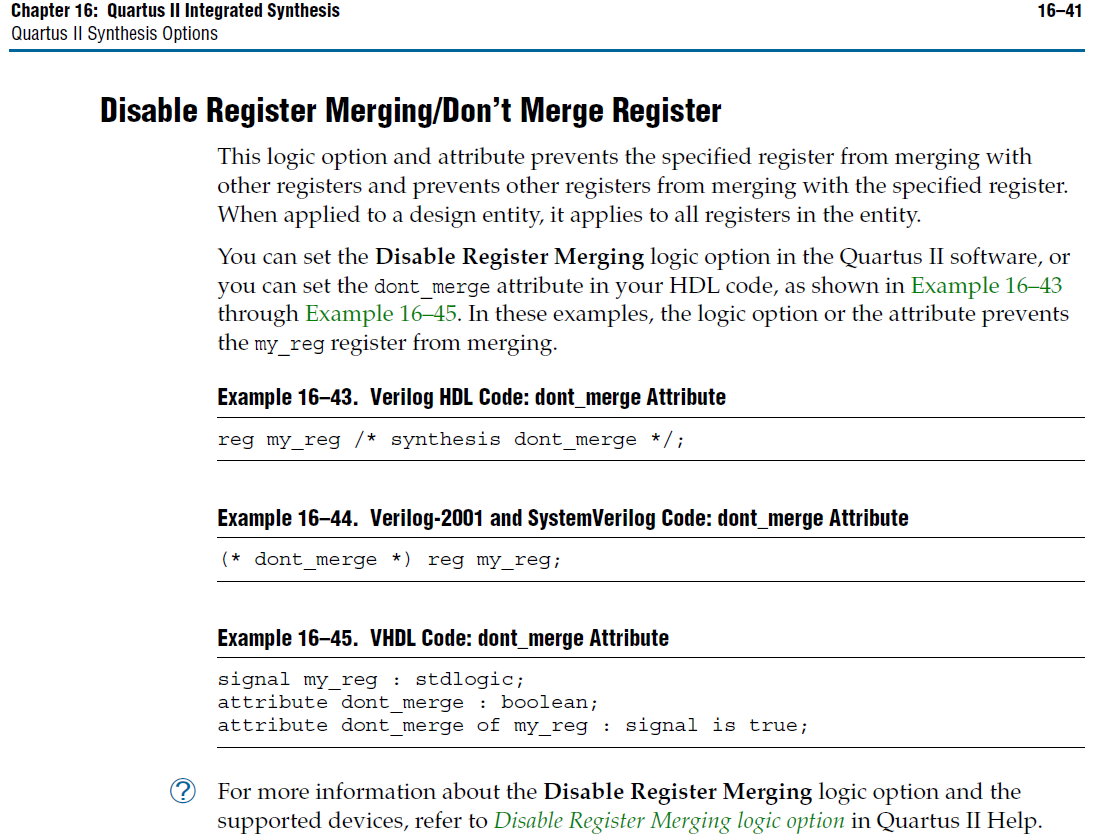

下面放的图片是官方文档16. Quartus II Integrated Synthesis文档中的内容,主要就是讲到了如何在HDL代码中添加一些内容防止被优化。

这个优化是默认开启的,并且对于Altera的任意芯片都适用,就是对在不同层次的相同输入寄存器进行合并。

对于这个选项的理解我现在也很肤浅,之后有更深入的了解也会及时在博客中进行更新。那么既然是优化选项,去掉了势必会有一些影响,那么来简单地看一下去掉这个优化选项之后,产生了什么影响呢。那么影响分好和坏两种,首先来说说好的影响,最明显的好处是综合时间缩短了,从原先的3个小时缩短到了现在的18分钟。那么带来了什么影响呢,很明显应该是资源增加了,那么哪些资源增加了,增加了多少呢。我们来看下面的这张表。

|

|

|

|

|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

从上面的表格中,可以看出不含优化的程序资源消耗只比优化之后的程序多了一点点,至少在我这个工程中是这样的,而这一点点资源的增加,相较于综合时间的大幅度提升,优化与否可想而知。

哦,对了,还有最重要的是,对运算结果是否有影响呢。很明显的,这只是一个优化选项,不影响结果,我们实际测试得到的也是相同的结论。

如何你觉得这个文章对你有帮助,支持一下作者~