CMOS反相器的传播延时取决于它分别通过PMOS和NMOS管充电和放电负载电容CL所需要的时间。说明使CL尽可能小是实现高性能CMOS电路的关键。

可以用以下方式减小一个门的传播延时:

(1)减小CL:该负载电容由三个主要部分组成:门本身的内部扩散电容、互联线电容和扇出电容。

(2)增加晶体管的W/L比

(3)提高VDD

反相器的延时只取决于它的外部负载电容与输入电容之间的比值。

动态功耗

由充放电电容引起的动态功耗

当电容CL通过PMOS管充电时,它的电压从0v升至VDD,此时从电源吸取了一定数量的能量。该能量的一部分消耗在PMOS器件中,其余存放在负载电容上。在由高至低的翻转器件,这一电容被放电,于是存放的能量被消耗在NMOS管中。

考虑由低至高的翻转。假设输入波形具有为零的上升和下降时间,或者说NMOS好PMOS器件不会同时导通。

在这一翻转期间从电源中取得的能量值EVDD以及在翻转结束时在电容上存储的能量Ec,通过在相应周期上对瞬时功耗积分求得:

直接通路电流引起的功耗

考虑一个静态CMOS反相器在输入端由0–>1的翻转。假设负载电容很大,所以输出的下降时间明显大于上升时间,这这些情况下输入在输出开始改变之前就已经通过了过渡区。由于这一时期PMOS器件的源–漏电压近似为0,因此该器件甚至还没用传导任何电流就断开了。这种情况下短路电流接近于0.

输出电容非常小,因此输出的下降时间明显小于输入的上升时间。PMOS器件的源–漏电压在翻转器件的大部分时间内等于VDD,从而引起了最大的短路电流(等于PMOS的饱和电流)。

总结:

使输出的上升/下降时间大于输入的上升/下降时间可以使短路功耗减到最小。但输出的上升/下降时间太大会降低电路的速度并在扇出门中引起短路电流。

短路电流的功耗可以通过使输入和输出信号的上升/下降时间匹配来达到最小。当负载电容太小时,功耗主要来自短路电流。负载电容非常大时,所有的功耗都用来充电和放电负载电容。如果使输入/输出的上升/下降时间相等,则大部分功耗与动态功耗有关,只有很小一部分是短路电流带来的功耗。

静态功耗

一个电路的静态功耗可以用下列关系来表示:

Pstat = Istat Vdd

Istat是在没有开关活动存在时在电源两条轨线之间流动的电流。

总会有泄漏电流流过位于晶体管源(或漏)与衬底之间的反相偏置的二极管,这一电路一般来说非常小。

结的泄漏电流是由热产生的载流子引起的。数值随着结温而增加,并且呈指数关系。

泄漏电流的一个突出来源是晶体管的亚阈值电流。泄漏电流的存在会减小噪声容限。

阈值电压Vt越高的单元,它的漏电功耗越低,但门延迟越长。

阈值电压Vt越低的单元,它的漏电功耗越高,但门延迟越短。

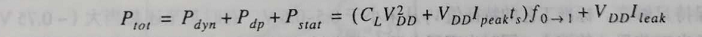

CMOS反相器的总功耗可以表示成三部分的和: