一、基本

1.5529包含五个时钟源

XT1CLK:外部低频晶振,32.786KHz,可以用作FLL参考电源,也可以整4MHZ到32Mhz

XT2CLK:外部高频晶振,可用作fll参考源可以4MHZ到32MHZ

但是F5529的最高CPU频率好像是25MHZ?

VLO:内部低耗低频晶振,10kHZ

REF:内部低频参考源,32.786Khz,可用作FLL参考源,精度高

DCO:数控振荡器,通过FLL设置

三个信号源

ACLK:辅助时钟源

MCLK:主时钟源

SMCLK:

时钟源和信号源的关系是,信号源来自于时钟源的分频。这三个时钟源可以选择从哪个时钟源里面得到时钟信号,并且自身还可以分频。于是可以获得多种多样的分频时钟。时钟源和信号源都可以给其下几个同时使用。当然信号源具体都能从哪几个时钟源中获得好像每个芯片不太一样,还是要看下 user’s guide

2.其中,选择XT1的时候需要将对应的IO设置为SEL=1,这个时候XT1clk才能够使用,否则无法使用

在f5529中,5.4为XT1的输入,5.5位XT1的输出

3.当设定完成后,如果没有时钟的设定,FLL将把MCLK和SMLCK设置为1.048576,DCO为2.097152,说明这个时候DCODIV其实是2

4.锁频环的设定

fdcoclk=D*(N+1)(fref/n)

fdcoclkdiv=(N+1)(fref/n)

二、寄存器设定

f5529一共有9个相关的寄存器

1、UCSCTL0

用于DCO的设定,在不使用FLL的时候,需要首先设定DCO和MOD,这个在g2553里面有直接的函数设定成为1、2、4、8MHZ,但是f5529好像并没有。这个其实是一个大致的范围,搞不太懂。在使用FLL的时候,这个会自动调整,所以如果用FLL的话,就只需要整成0x00应该就行了。

2、UCSCTL1

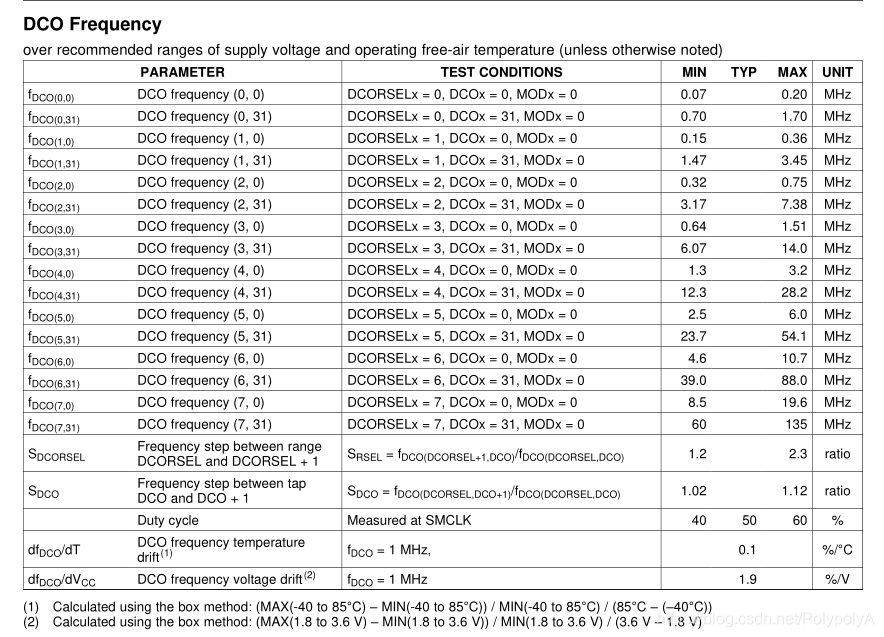

DCORSEL:选择DCO的范围,在使用FLL的时候,需要先规定一个范围,这个范围必须将我们所要想达到的频率包括进去,否则应该会出错误。

DCOMOD:是否调制?这个PUC后是0,允许调制,是是否FLL调制还是?不管先

DCO的范围我在DATASHEET里面找到的

3、UCSCTL2

FLLD:D的确定,D其实是分频系数,可以选择12481632次分频

FLLN:就是公式里面N的值范围是0-9,共10位,最高1024

4、UCSCTL3

SELREF:FLL的参考时钟的选择,选择REFOCLK或者XT1CLK是比较常见的32.786kHZ

FLLREFDIV:FLL参考时钟分频,这样的话参考时钟也就能够改变来适应

5、UCSCTL4

SELA:选择ACLK的时钟源

SELS:选择SMCLK的时钟源

SELM:选择MCLK的时钟源

6、UCSCTL5

DIVPA:对于外部管脚的分频?把频率传输给外部管脚,我其实不太明白

DIVA\DIVS\DIVM是对应的分频

7、UCSCTL6

XT2和XT1的相关的寄存器,先不看

8、UCSCTL7

相关时钟的错误标志,当各个时钟出错的时候会置位

看见例程中有这么一段

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

在设定锁频环之前,先让各个时钟稳定,然后在使用锁频环

9、UCSCTL8

信号请求使能

各种时钟的REQEN,之前看到的在不同的模式下,在不同的供电模式中有不同的选择,具体可以看user’s guide 166页

10、UCSCTL9

BYOASSLV:旁路模式输入摇摆电平范围

不太清楚有啥用,目前好像不太需要配置

三、用FLL配置DCO

目前来说还是DCO用的比较多,所以通过FLL来得到DCO还是比较重要的,g2553上没有FLL,就很迷

大致的步骤,来自例程MSP430F55xx_UCS_02

1、选择FLL参考源

UCSCTL3 = SELREF_2; // Set DCO FLL reference = REFO,选择REFO来作为参考

2、检测时钟源是否稳定

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

这个例程里面实际上只需要检测DCO的就行了,不过无所谓,以后直接粘上去就行了

这一步好像也不是必要的

3、关闭FLL控制,好像如果不关闭的话,FLL寄存器不会改变

__bis_SR_register(SCG0); // Disable the FLL control loop

4、选择DCO的范围,设定DCO的D、N

UCSCTL1 = DCORSEL_5; // Select DCO range 16MHz operation

UCSCTL2 |= 249; // Set DCO Multiplier for 8MHz

// (N + 1) * FLLRef = Fdco

// (249 + 1) * 32768 = 8MHz

计算公式就是这样

fdcoclk=D*(N+1)(fref/n)

fdcoclkdiv=(N+1)(fref/n)

5、开启FLL

__bic_SR_register(SCG0); // Enable the FLL control loop

6、等待DCO稳定

计算公式是

n x 32 x 32 x f_MCLK / f_FLL_reference

这个里面等待的时间是

32 x 32 x 8 MHz / 32,768 Hz = 250000

所以加一个句子

__delay_cycles(250000);

初学MSP430F5529时钟以及FLL配置

猜你喜欢

转载自blog.csdn.net/PolypolyA/article/details/100663289

今日推荐

周排行