MSP430F5529 上手小例程4

*将ACLK和SMCLK配置为REFCLK、VLOCLK

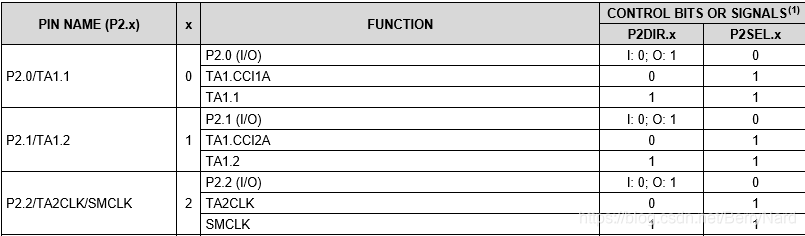

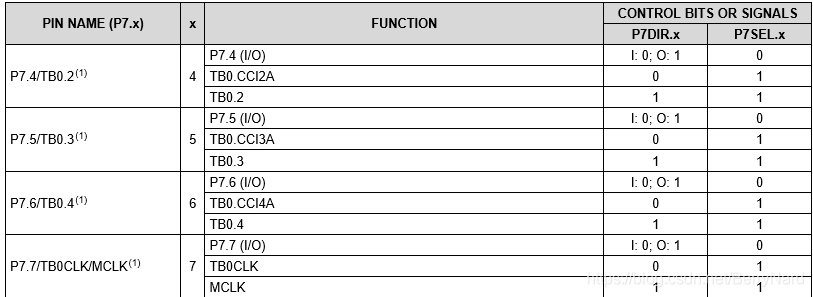

*datasheet的打开方式

查阅资料得知:

3个时钟源:

REFO: 32.768KHZ

VLO: 10KHZ

XT2: 4MHZ

LFXT1: 32.768KHZ

DCO: 通过FLL设置,经1、2、4、8、16、32分频可得到DCOCLKDIV

XT1和XT2必须进行PXSEL配置,否则无效。

系统稳定后,DCOCLK默认2.097152MHZ,FLL默认二分频,则MCLK和SMCLK的频率为1.048576MHZ

3个时钟信号:

ACLK:开机默认XT1,低频切换REFO,其他DCO

MCLK:开机默认DCOCLKDIV

SMCLK:开机默认DCOCLKDIV

不知道是不是大家也和我一样,在刚开始的时候对datasheet并不感冒,但用到了就发现还是有很大用处滴。

就是从上面的数据表中我们找到了设置PxDIR和PxSEL的值,来选择第二功能。

代码很简单,如下1

#include <msp430.h>

/**

* main.c

*/

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // stop watchdog timer

P1DIR |= BIT0; //设置为输出

P1SEL |= BIT0; //ACLK输出端,用来测量频率

P2DIR |= BIT2;

P2SEL |= BIT2; //SMCLK

P7DIR |= BIT7;

P7SEL |= BIT7; //MCLK

UCSCTL4 = UCSCTL4&(~(SELS_7|SELM_7)) | SELS_2 | SELA_1;

//USCTL4&(~(SELS_7|SELM_7))表示将SELS和SELM清零

while(1);

return 0;

}

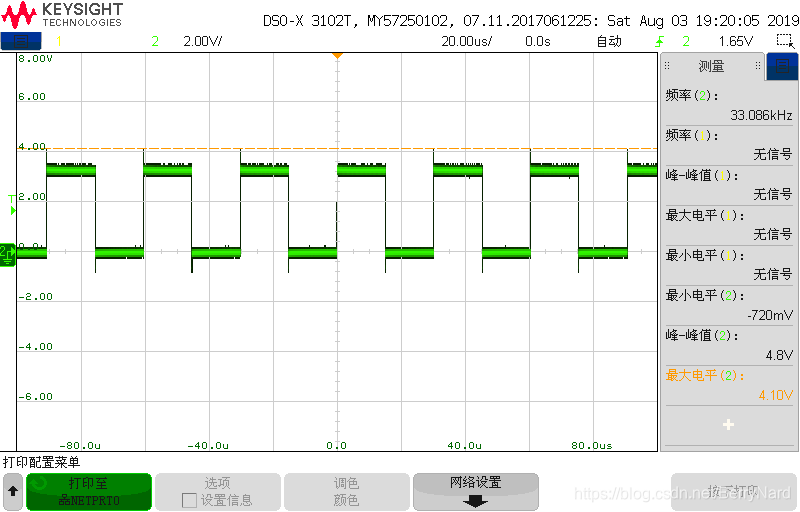

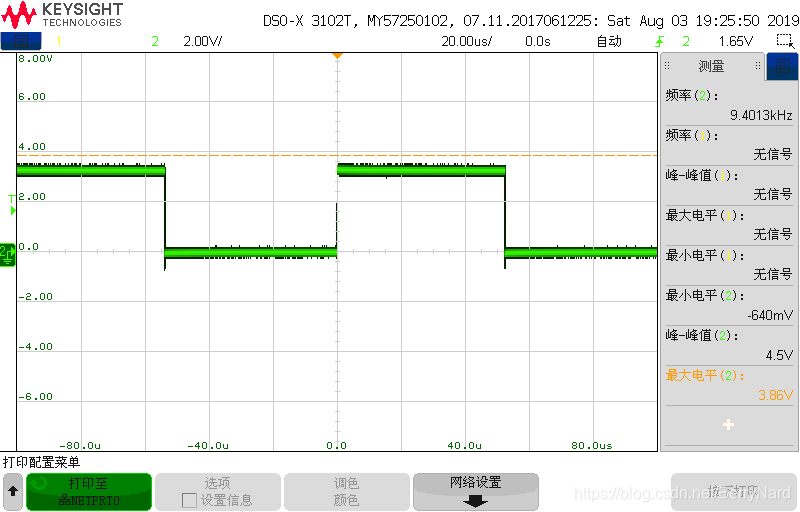

上图

33.086KHZ,很接近REFO=32.768KHZ

9.4013KHZ,也很接近VLO=10KHZ

代码来自:https://download.csdn.net/download/berrynard/11426569

博主是个搬运工并实践了一下??? ↩︎ ↩︎