采样保持放大器

THA性能参数

1.捕获时间(tAQ):接到跟踪命令后直到能在规定的误差范围内跟踪vI的时间。在进入保持模式之前必须完全捕获输入。

2.缝隙时间(tAP):在接到保持命令一段时间后才能停止对vI的跟踪。这段时间就是缝隙时间。

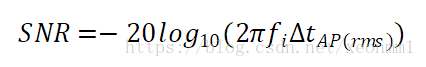

3. 缝隙不确定时间(ΔtAP):如果通过将保持命令提前tAP来补偿tAP,那么就确定了最终的时序误差,以及对于给定分辨率下的最大采样频率。缝隙跳动导致了输出误差ΔvO=(dvi/dt) ΔtAP,这表明可以把实际的已采样的波形看成是理想采样波形与噪声分量的叠加。另一种理想采样电路的输入是频率为fi的正弦波,它的信噪比:

4.保持模式建立时间(ts):在接到保持命令后,需要一段时间才能稳定。

5.保持阶跃。由于寄生开关电容的影响,当电路进入保持模式以后,就会在开关驱动器和CH之间出现不希望的电荷转移。对应的变化的ΔvO成为保持阶跃、消隐误差,或采样保持失调

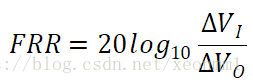

6.馈通。在保持模式期间,vO应与vI的任何变化无关。实际上,由于开关上杂散电容的影响,存在着少量的交流耦合,称为馈通。SW上的杂散电容与CH组成了一个分压器,因此输入变化ΔvI产生ΔvO=[CSW/(CSW+CH)]ΔvI的输出变化。馈通抑制比:

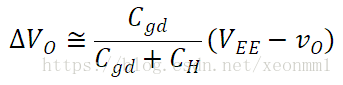

7.电压降。如果要获得快速的捕获特性,而必须把CH保持在很低的水平上时,电压降就是主要的考虑因素。对于JEFT开关的情况,馈通是由漏极和源极电容Cds引起的。而保持阶跃是由栅极和漏极电容Cgd引起的。通常在皮法范围内。当驱动器将栅极直接由接近vO拉至接近VEE时,它会从CH上移除ΔQ=Cgd(VEE-vO)。产生的保持阶跃为:

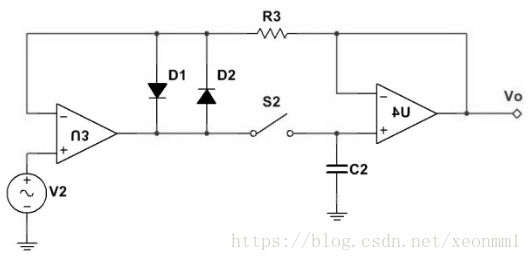

减小保持阶跃技术:

1.利用CMOS传输栅来实现开关,采用反相信号对两个FET进行驱动,一个FET会注入电荷另一个会移出电荷。

2.利用驱动栅负阶跃产生一个点荷包通过电容注入CH。

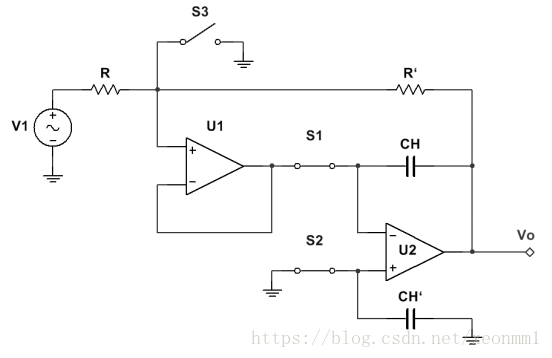

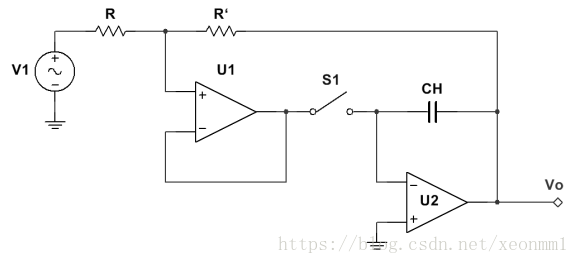

积分型THA

如果开关工作在虚地的模式下,可以显著简化电荷补偿。在这种情况下由于保持电容位于输出放大器的反馈通路上,所以将它称为积分型THA。由于开关一直虚地,那么从求和节点经移出的电荷就是一个常数,和输出无关。可以通过调整U1的失调控制。

改进后: