Mux相关电路生成器。

参考链接:

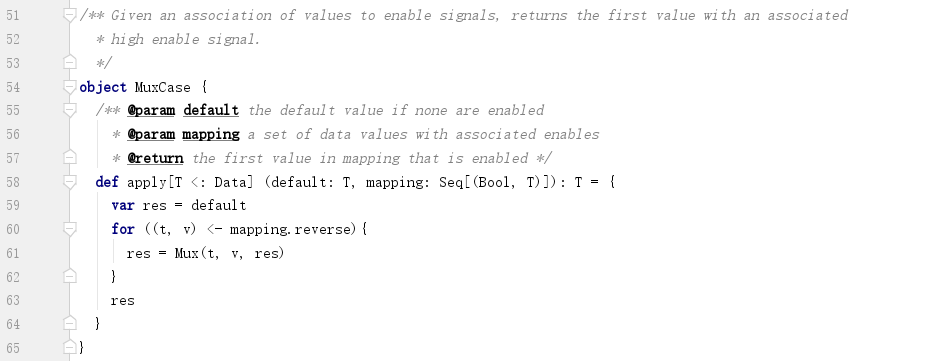

1. MuxCase

按在mapping中的顺序为优先顺序,若前一个元素的Bool为真,则返回该元素的T;否则,看下一个元素。若所有元素的Bool都为假,则返回default。

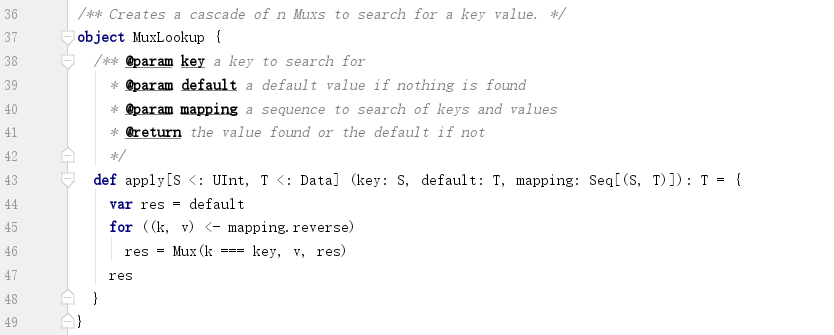

2. MuxLookup

与MuxCase类似,不同点在于mapping的Key不是Bool,而是S类型,需要与key进行比较。

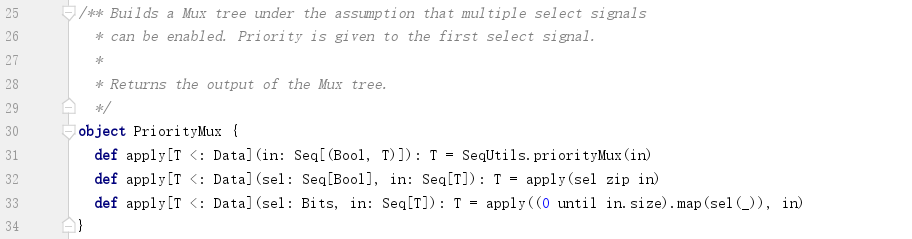

3. PriorityMux

1) 第三个apply委托给第二个apply

(0 until in.size).map(sel(_))逐个取出sel中的每一位,作为Bool返回;

2) 第二个apply委托给第一个apply

sel zip in 把每个序列中的相同序号的元素提取出来组合成一个元组,最终形成一个元组的序列;

3) 第一个apply

使用递归实现低序高优先的级联选择器。

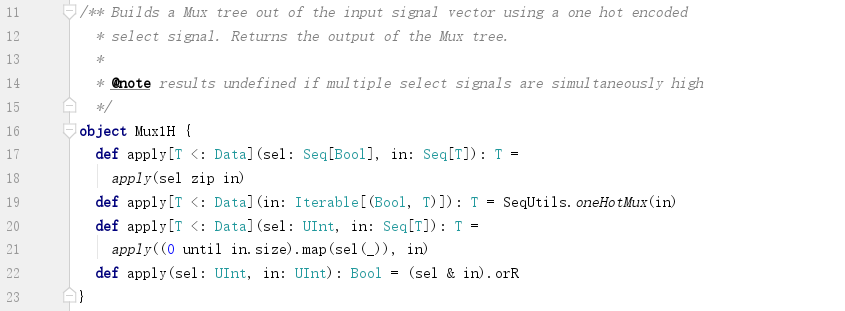

4. Mux1H

使用独热码(one hot)编码选择参数(Seq[Bool]),意即其中只有一个为真,其他都为假。

1) 第一个apply委托给第二个apply

2) 第三个apply委托给第一个apply

3) 第四个apply: def apply(sel: UInt, in: UInt): Bool = (sel & in).orR

返回sel选中的比特是1还是0;

4) 第二个apply: def apply[T <: Data](in: Iterable[(Bool, T)]): T = SeqUtils.oneHotMux(in)

返回Bool为真的T。根据假设只有一个元组的Bool为真。

实现比较复杂,这里不再展开。

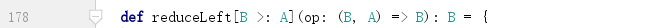

PS. reduceLeft从左到右逐个把所有元素提取出来参与op运算。第一次提取的为前两个元素:

5. 附录