由于一般的晶振受限于工艺与成本,做不到很高的频率,可在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路来实现稳定且高频的时脉冲讯号。

本例通过MC9S12XS128这款单片机来展示如何配置锁相环并为总线提供时钟。

一般需要以下几步来进行配置:

1.总线时钟选择外部晶振,通过CLKSEL_PLLSEL配置,为0时,总线时钟来源于外部晶振;为1时,总线时钟来源于PLLCLK。

2.关闭IPLL,通过PLLCTL_PLLON来配置,为1时,打开IPLL;为0时,关闭IPLL。

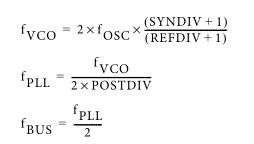

3.配置PLL的频率,通过SYNR、REFDV和POSTDIV来配置,有如下计算公式进行计算。

常用频率的几个赋值数据(POSTDIV = 0x00,此时f PLL = f VCO)

busclk SYNR REFDV

16M 00|01 80|01

32M 40|03 80|01

40M c0|01 80|01

48M c0|05 80|01

64M c0|07 80|01

80M c0|09 80|01

88M c0|0a 80|01

96M c0|0b 80|01

104M c0|0c 80|01

120M c0|0d 80|01

4.打开IPLL,通过PLLCTL_PLLON来配置,为1时,打开IPLL;为0时,关闭IPLL。

5.判断PLL是否稳定,通过CRGFLG的LOCK位来确定,为1时,PLL稳定;为0时,PLL不稳定。

6.选择PLL作为时钟源,通过CLKSEL_PLLSEL位来配置。

以下为INIT_PLL的代码

void INIT_PLL(void)

{

CLKSEL_PLLSEL=0; //选择外部晶振作为总线时钟

PLLCTL_PLLON=0; // 先关闭PLL

SYNR=0x40 | 0x03;

REFDV=0x80 | 0x01;

POSTDIV=0x00; //配置PLL完成,此时PLL为64MHz

PLLCTL_PLLON=1; //打开PLL

_asm(nop);

_asm(nop); //等待两个机器周期

while(CRGFLG_LOCK==0); // 确定PLL是否稳定 LOCK=1 稳定,=0 不稳定

CLKSEL_PLLSEL =1; //选择PLL作为时钟源,busclock = 32MHz

}