最近在看系统时钟,网上找了几篇关于锁相环资料,拼了一篇文档,觉得自己看明白了,分享出来

(一) PLL(锁相环)电路原理

在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一 PLL(锁相环)电路的基本构成

PLL(锁相环)电路的概要

图1所示的为PLL(锁相环)电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。)

利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。在此一电路中,假设fr>fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果fr<fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。如果有相位差存在时,便会产生正或负的脉波输出。)

此一PD脉波信号经过回路滤波器(LoopFilter)的积分,便可以得到直流电压VR,可以控制VCO电路。

由于控制电压vr的变化,VCO振荡频率会提高。结果使得fr=f0在f与f0的相位成为一致时,PD端子会成为高阻抗状态,使PLL(锁相环)被锁栓(Lock)。

相位比较器的工作原理

此所说明的相位比较器为相位.频率比较器(PFC:Phase-Frequency Comparator)之型式,后述之LSIMC145163P便内藏有此一电路。

此一型式的相位此较器并非只做 相位的比较,也即是,并非只做之比较,在频率f不同的场合,也可以做为频率比较器工作原理。

相位的比较,也即是,并非只做之比较,在频率f不同的场合,也可以做为频率比较器工作原理。

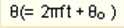

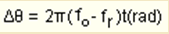

所谓相位差利时△与时间t的关系为

在只做相位检出的场合,例如,可能分辨不出是延迟300°或前进60°。可是,在相位-频率比较器中,如果fr>fo则被视为是相位延迟。

回路滤波器的选择方法

回路滤波器的时间常数与PLL(锁相环)控制的良否有很大的关系。其详细的计算方法虽然不在此说明,但是,基准频率fr为l0kHz时,输往回路滤波器的脉波周期为0.1mS。

为了保持电压值VR而增大回路滤波器的时间常数时,便无法追踪VCO的振荡频率的变化。如果时间常数太小时,会在VR上出现涟波,使PLL(锁相环)的稳定度恶化。

因此,根据经验,回路滤波器的时间常数,选择大约为基准频率的周期(1/fr)的数百倍。在此选择约为数十mS。

(二)

锁相环是一种控制晶振使其相对于参考信号保持恒定相位的电路,在数字通信系统中使用比较广泛。目前微处理器或DSP集成的片上锁相环,主要作用则是通过软件实时地配置片上外设时钟,提高系统的灵活性和可靠性。此外,由于采用软件可编程锁相环,所设计的系统处理器外部允许较低的工作频率,而片内经过锁相环微处理器提供较高的系统时钟。这种设计可以有效地降低系统对外部时钟的依赖和电磁干扰,提高系统启动和运行的可靠性,降低系统对硬件的设计要求。

TMS320F28l2处理器的片上晶振和锁相环模块为内核及外设提供时钟信号,并且控制器件的低功耗工作模式。片上晶振模块允许使用2种方式为器件提供时钟,即采用内部振荡器或外部时钟源。如果使用内部振荡器,必须在XI/XCLKIN和X2这两个引脚之间连接一个石英晶体,一般选用30MHz。如果采用外部时钟,可以将输人的时钟信号直接接到XI/XCLKIN引脚上,而X2悬空,不使用内部振荡器。晶体振荡器及锁相环模块结构如图1 所示。

外部XPLLDIS引脚可以选择系统的时钟源。当XPLLDIS为低电平时,系统直接采用外部时钟或外部晶振作为系统时钟;当XPLLDIS为高电平时,外部时钟经过PLL倍频后为系统提供时钟。系统可以通过锁相环控制寄存器来选择锁相环的工作模式和倍频的系数。表1列出了锁相环配置模式。

锁相环模块除了为C28x内核提供时钟外,还通过系统时钟输出提供快速和慢速2种外设时钟,如图2所示。而系统时钟主要通过外部引脚XPLLDIS及锁相环控制寄存器进行控制。因此,在系统采用外部时钟并使能PLL(XPLLDIS=1)的情况下,可以通过软件设置C28x内核的时钟输人。

如果XPLLDIS为高电平,使能芯片内部锁相环电路,则可以通过控制寄存器PLLCR软件设置系统的工作频率。但要注意,在通过软件改变系统的工作频率时,必须等待系统时钟稳定后才可以继续完成其他操作。此外,还可以通过外设时钟控制寄存器使能外设时钟。在具体的应用中,为降低系统功耗,不使用的外设最好将其时钟禁止。外设时钟包括快速外设和慢速外设两种,分别通过HISPCP和LOSPCP寄存器进行设置。下面给出改变锁相环倍频系数和外设时钟的具体应用程序。

参考文献:

https://blog.csdn.net/leoufung/article/details/50268031

后续:

每个模块的简单原理描述如下:

鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

分类

按照实现技术,可以分为模拟锁相回路(Analog PLL)和数字锁相回路(Digital PLL)。

按照反馈回路,可以分为整数倍分频锁相回路(Integer-N PLL)和分数倍分频锁相回路(Fractional-N PLL)。

按照鉴频鉴相器的实现方式,可以分为电荷泵锁相回路(Charge-Pump PLL)和非电荷泵锁相回路。

按照环路的带宽,它可以分为宽带锁相回路(Wide band loop PLL)和窄带锁相回路(Narrow band loop PLL)。