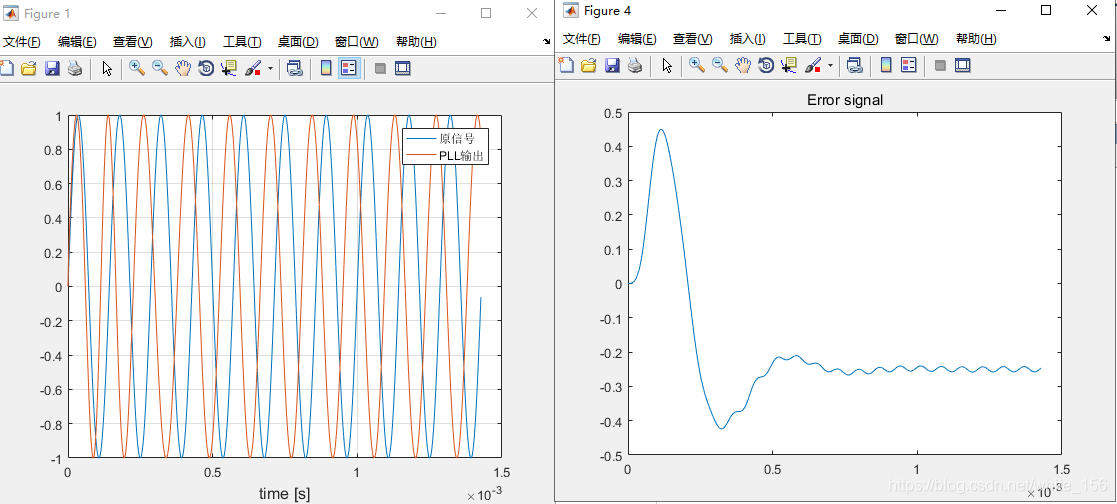

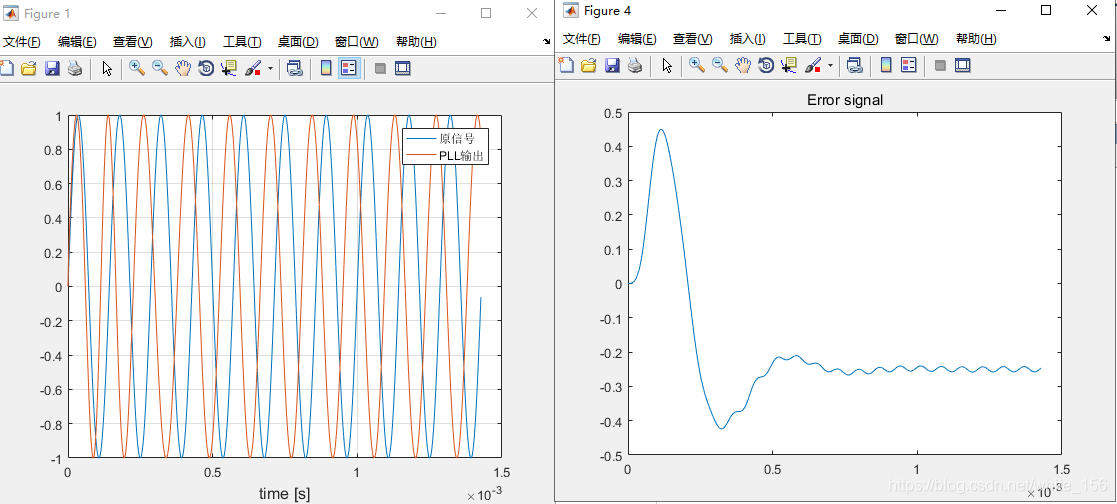

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

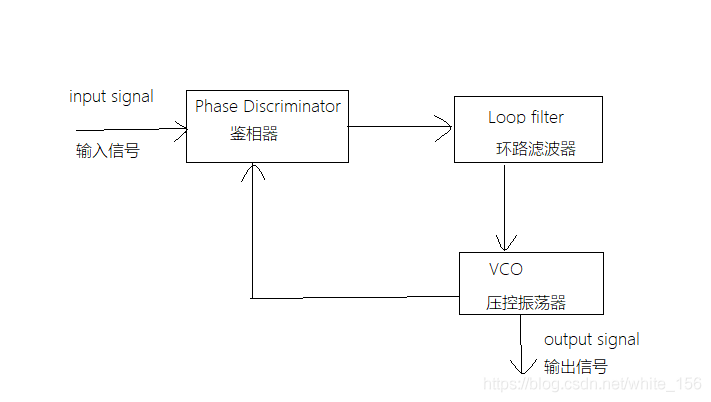

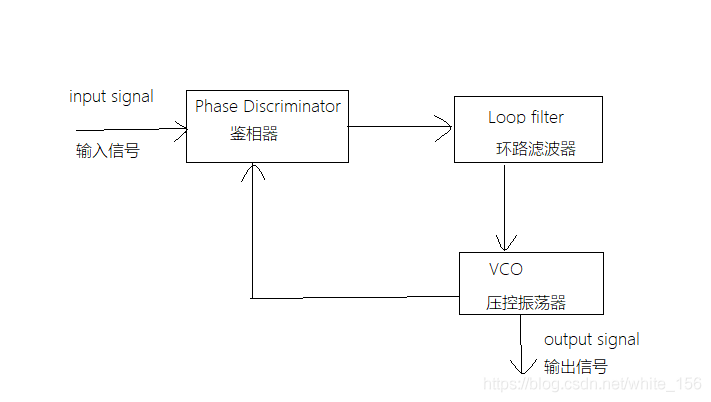

PLL工作原理框图如下

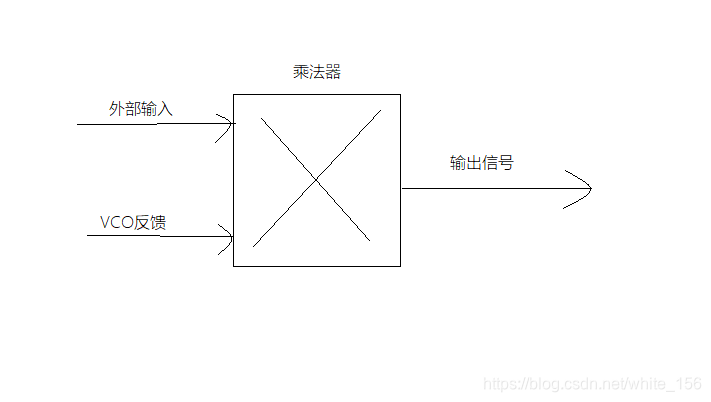

首先说明鉴相器Phase Discriminator:

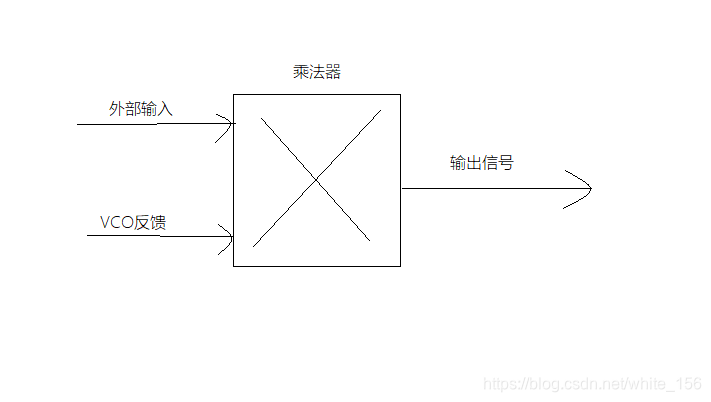

鉴频器可以由乘法器实现

设外部输入为

Ui(t)=Umsin[ωit+θi(t)],VCO直流输出(无外接信号时输出)为

Uo(t)=Uomcos[ωot+θo(t)],两信号相乘后积化和差得

21UmUom{sin[ωit+θi(t)+ωot+θo(t)]+sin[ωit+θi(t)−ωot−θo(t)]}

这样就是鉴频器所产生的输出信号

接下来再看环路滤波器,这个实际上就是个LPF,为了滤除鉴频器所产生的和频率信号

sin[ωit+θi(t)+ωot+θo(t)],经过LPF之后,就只剩下低频的差信号,也就是输入信号与VCO信号的相位差

sin[(ωi−ωo)t+θi(t)−θo(t)]

最后,我们再看这个相位差又是如何影响VCO,这里我们不妨对相位差做分类讨论,设相位差为

Δθ(t)

-

Δθ(t)<0

此时输入信号滞后于VCO输出,

sinΔθ(t)<0,VCO输入为负,导致输出信号频率下降,更加靠近输入信号频率

-

Δθ(t)=0

此时输入信号与VCO输出同相位,无输入信号,输出不变,仍保持为输入信号频率

-

Δθ(t)>0

此时输入信号超前于VCO输出,

sinΔθ(t)>0,VCO输入为正,导致输出信号频率上升,更加靠近输入信号频率

之后VCO输入再接入到鉴相器中,继续比较与外部输入的相位差.

因此我们可以看到,PLL在不断接近输入信号的频率,当与输入信号同频则保持锁定.