物理约束

在写.sdc约束文件时,要做的第一件事情就是使用create_clock对进入FPGA的时钟进行约束。其语法格式如下:

create_clock[-add] [-name <clock_name>] -period <value> [-waveform<edge_list>] <targets>

参数解释:

-name表示生成的时钟名称

-period表示时钟周期,单位为ns

-waveform可以详细描述时钟占空比及其上下移位置

<targets>端口列表

-add用于为一个端口添加多个时钟约束

例子:

create_clock-period 10 -name clk_100 [get_ports clk]

生成了一个周期为10ns占空比为50%的时钟,其名字为clk_100,其端口名为clk

create_clock-period 10 -waveform {8 12} -name clk [get_ports clk]

生成一个周期为10ns上升沿8ns,下降沿2ns的时钟

create_clock-period 10 -name clk_100 [get_ports clk]

create_clock-perioid 6.6 -name clk_150 -add [get_ports clk]

在clk一个端口上生成两个时钟,其周期分别为10ns和6.6ns。如果一个系统中同一个端口在不同时刻会有多种时钟输入,可以使用-add参数。否则,如果不添加-add参数,后面定义的时钟无效。

注1:

在Tcl语法中[]表示命令替换,因此[get_portsfpga_clk]将执行一个命令找到设计中与fpga_clk名字相符的端口。

注2:

Tcl与SDC是大小写敏感的,因此需确认fpga_clk与设计中的端口名称完全一致的

详细了解FPGA selectIO是学习FPGA基础,FPGA IO接口标准约束了IO的实现方式。大的分类:单端信号:LVCOMS、LVTTL;差分信号:SSTL、HCTL、LVDS、CML等,注意IO bank的VREF使用

I/O接口标准

1.单端信号接口标准

LVTTL和LVCMOS(JESD8-5,JESD8-B)

SSTL(JESD8-8,JESD8-9B,JESD8-15)

HSTL(JESD8-6)

LVTTL和LVCMOS结构通常是简单的push-pull。最简单的例子就是CMOS反向器,需要满足的唯一参数是VIL/VIH,VOL/VOH以及驱动电流,接口标准相对易于实现。其输入和输出参数见下面的表格。随着VDD范围的不同,参数有所不同。

SSTL(Stub Series TerminatedLogic)有三种:SSTL_18,SSTL_2,SSTL_3。SSTL不同于LVTTL和LVCMOS的一个重要方面是SSTL要求传输线终端匹配。所以,SSTL有输出阻抗参数以及不同的终端匹配方法。这个差异对高速信号来说是非常重要的,因为合适的的终端匹配可以减少反射减少EMI并改善稳定速度提高定时裕度。LVTTL和LVCMOS信号也可以进行终端匹配,但是因为这个要求并没有清晰地在参数中说明,对于终端匹配电阻对信号摆动的影响用户需要仔细调整。

SSTL与LVTTL驱动器没有太多的不同,但是输入缓冲却非常不同。SSTL输入是查分对,因此输入级提供较好的电压增益以及较稳定的阈值电压,这使得对小的输入电压摆幅具有比较高的可靠性。如图1所示。

下面的表是关于SSTL的电源和输入参数,注意,SSTL对于不同类型的驱动器有不同的参数。SSTL_3和SSTL_2定义2类驱动器,以区别不同的终端匹配方案。SSTL_18没有明确的类型定义,但是,取决于终端环境,驱动器必须能够在输入缓冲处产生相应的电压摆幅。建议用户参考相关标准。

AC参数指的是一个阈值电压,当信号跨越这个阈值电压时,接收器状态一定会发生改变。只要输入保持在定义的DC阈值之上,接收器将维持逻辑状态不变。这有利于系统设计者对整个系统性能进行优化。

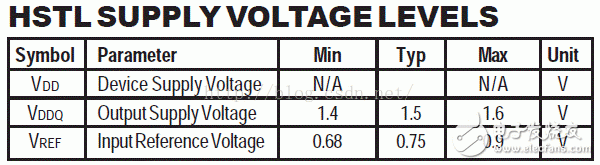

HSTL(High-SpeedTransceiver Logic)是另外一个标准,与SSTL一样,HSTL输入级使用差分放大器,类似于SSTL,HSTL有输出电压和器件电压,允许这两个电压不同。

TTL,CMOS以及LVTTL,LVCMOS

TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本。TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大,但功耗大。CMOS是MOS管逻辑,为压控器件,且输入电阻极大,CMOS电平器件速度慢,驱动能力不足TTL,但功耗小。正是由于CMOS器件输入阻抗很大,外界微小的干扰就有可能引起电平的翻转,所以CMOS器件上未使用的输入引脚应做上下拉处理,不能浮空。

由于TTL和CMOS电平在0或1时不一样,所以需要满足VOH(发送方) > VIH(接收方),且提供一定的噪声容限,发送方VOL小于接收方VIL,且提供一定的噪声容限。

高逻辑电平驱动低逻辑电平时,可串联50~330Ω电阻进行电平的转换。其中JTAG就是一个例子,在使用Cyclone III代芯片时,JTAG为2.5V电平,而Cyclone III是3.3V电平,使用时需要串接电阻,以实现电平的转换。串联电阻有时对于驱动能力较强的元器件如74LVT系列,为了消除信号振铃,可以串联电阻消除信号振铃现象。

与驱动能力相关的两个名词:拉电流与灌电流。

拉电流:拉电流是指电流方向为负,电流流出器件,称为拉电流,比如IOH;

灌电流:灌电流指的是电流方向为正,电流流入器件,称为灌电流,比如IOL;

Bipolar工艺的器件,特点是速度高,驱动能力强,但功耗大;CMOS工艺的器件,驱动能力和速度较Bipolar弱,但其集成度高,功耗低;而BiCMOS兼有Bipolar和CMOS的优势。

CMOS和TTL不适合高速电路原因

1)电平幅度较大,即使是低电平版本,摆幅也到了3.3V或2.5V,因此信号变化沿所耗费的时间越长,不适合于传输频率达到200MHz以上的信号。

2)输出信号为单端。在传输路径上易受到干扰,不利于远距离的传输

3)功耗较大。

1.RS232电平

或者说串口电平,有的甚至说计算机电平,所有的这些说法,指得都是计算机9针串口 (RS232)的电平,采用负逻辑,

-15v~ -3v 代表1

+3v~ +15v 代表0

2.RS485电平 和 RS422电平

由于两者均采用差分传输(平衡传输)的方式,所以它们的电平方式,一般有两个引脚 A,B

发送端 AB间的电压差

+2 ~ +6v:1

-2 ~ -6v:0

接收端 AB间的电压差

大于 +200mv 1

小于 -200mv 0

定义逻辑1为B>A的状态;

定义逻辑0为A>B的状态。

AB之间的电压差不小于200mv。