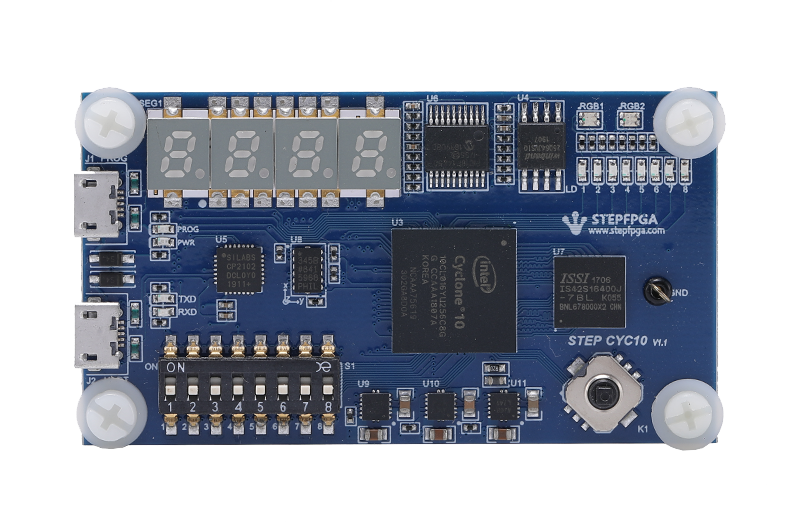

FPGA小脚丫开发板学习笔记:1位全加器设计

板子:Altera Cyclone10 STEP小脚丫FPGA开发板

IDE:QuartusII 18.1(Educational)

仿真软件:Modelsim-Alterl

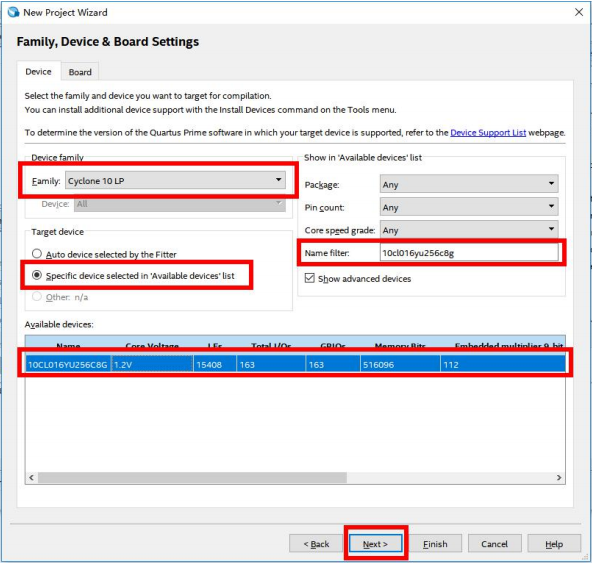

芯片系列:Cydone 10 LP

芯片名称:10CL016YU256C8G

芯片核心:10CL016

文章目录

〇、全加器

1. 全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

module FA_struct (A, B, Cin, Sum, Count);

input A;

input B;

input Cin;

output Sum;

output Count;

wire S1, T1, T2, T3;

// -- statements -- //

xor x1 (S1, A, B);

xor x2 (Sum, S1, Cin);

and A1 (T3, A, B );

and A2 (T2, B, Cin);

and A3 (T1, A, Cin);

or O1 (Count, T1, T2, T3 );

endmodule

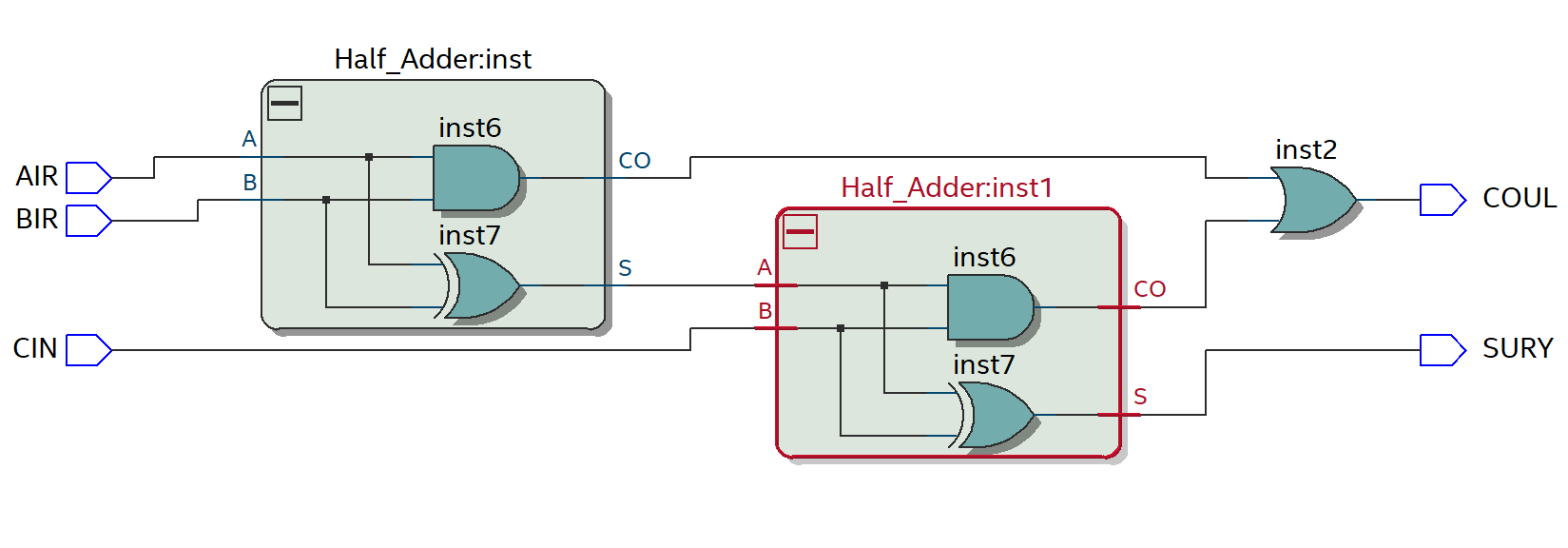

该实例显示了一个全加器由两个异或门、三个与门、一个或门构成 (或者可以理解为两个半加器与一个或门的组合)。S1、T1、T2、T3则是门与门之间的连线。代码显示了用纯结构的建模方式,其中xor 、and、or 是Verilog HDL 内置的门器件。以 xor x1 (S1, A, B) 该例化语句为例:xor 表明调用一个内置的异或门,器件名称xor ,代码实例化名x1(类似原理图输入方式)。括号内的S1,A,B 表明该器件管脚的实际连接线(信号)的名称,其中 A、B是输入,S1是输出。

2. 一位全加器

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

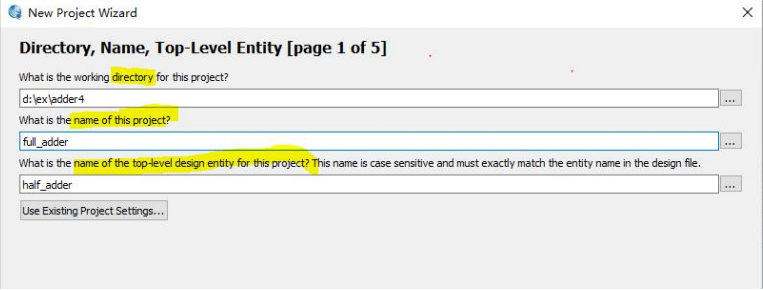

一、New一个

1. 新建工程

-

file->new project wizard->next->next

-

输入文件名(文件名不要用数字开头,否则会编译出错),选择存储路径

-

选择目标芯片:Cydone 10 LP系列的10CL016YU256C8G ,如图:

-

直接next,之后到达完成界面,这里会看见关于整个工程的一些信息,核对

一下是否正确,然后点击“finish”。

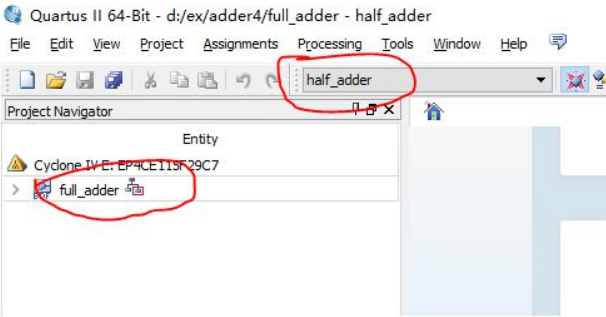

此时界面上会出现顶层文件名和项目名:

3

3

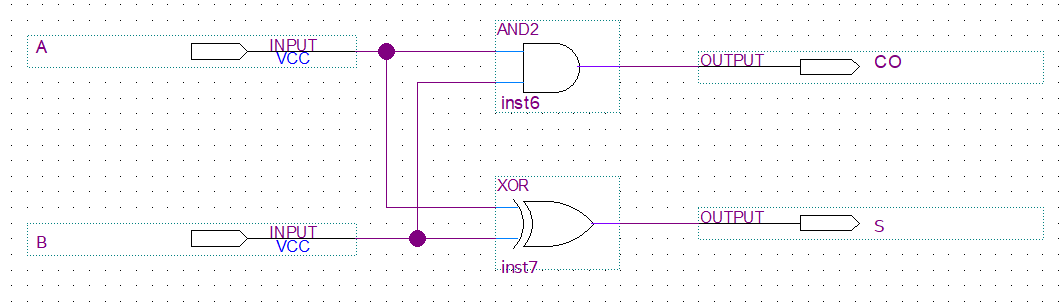

2. 绘制半加器原理图

原理图编辑输入流程如下:

- 新建原理图文件。打开QuartusII,选菜单“File”一“New”,在弹出的“New-”对话框中选择“ Design Files” 的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

- 在编辑窗中调入元件,完成半加器的原理图输入。

点击按纽“  ”或直接双击原理图空白处,从“ Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b, co和s。

”或直接双击原理图空白处,从“ Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b, co和s。

-

存盘编译。选择菜单File - Save As,选择刚才为自己的工程建立的目录d:\adder4,将已设计好的原理图文件取名为:half_adder.bdf(注意默认的后缀是.bdf),并存盘在此文件夹内。然后点击

进行编译,若无错误则可进行下一步,若有错进行原理图修改。编译完成后最下面的“message”框中会显示编译结果,没有error就可以忽略。

进行编译,若无错误则可进行下一步,若有错进行原理图修改。编译完成后最下面的“message”框中会显示编译结果,没有error就可以忽略。 -

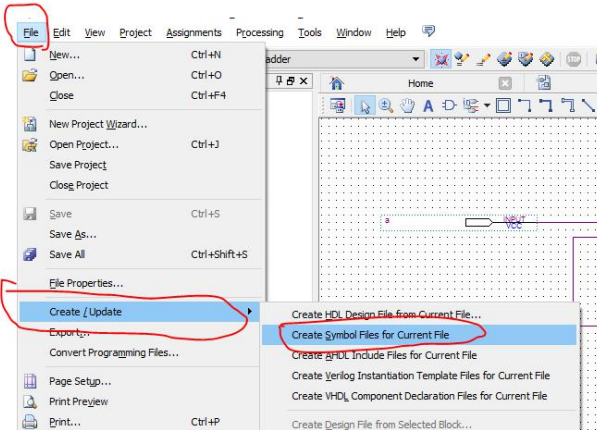

将项目设置为可调用元件

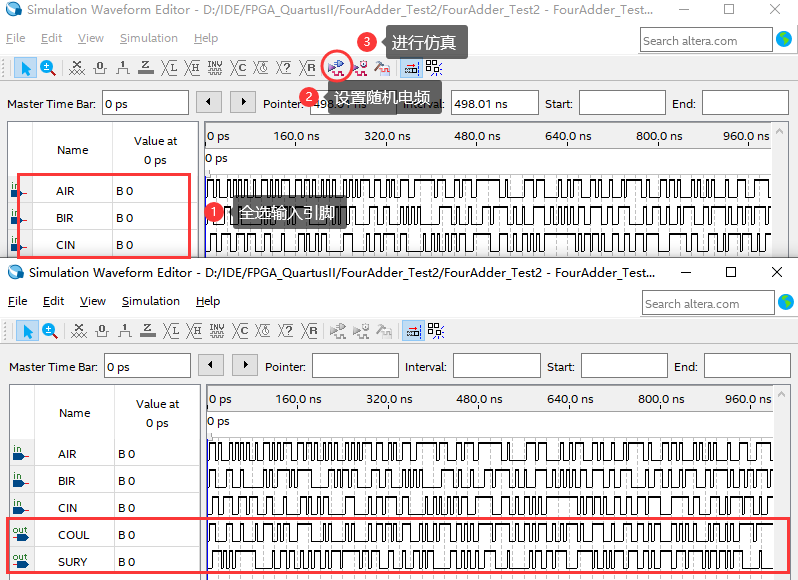

3. 波形仿真

-

新建波形文件。如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。点击“OK”。

-

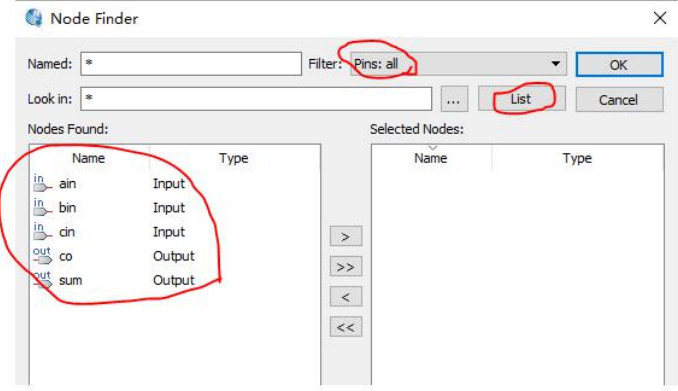

输入波形文件。在波形文件编辑器左端大片空白处双击,出现“insert node or bus”对话框,点击“node finder”按钮。如图。然后在随后出现的“node finder”对话框中点击“list”按钮,则半加器中所有的输入输出引脚全部出现在对话框左边。

-

再在该界面上点击“>>”,则把左边所有的端口都选择到右边,进入波形。

-

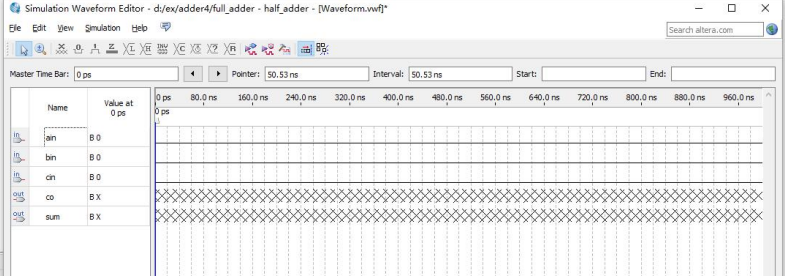

点击OK后出现如图的波形文件

-

使用Random控制输入电频,使其随机输入

-

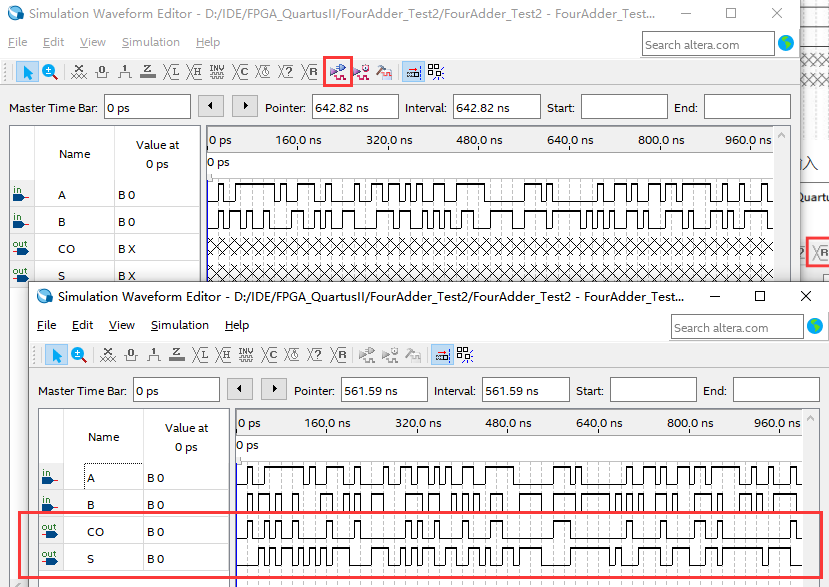

点击仿真按钮,进行仿真,得到如下结果

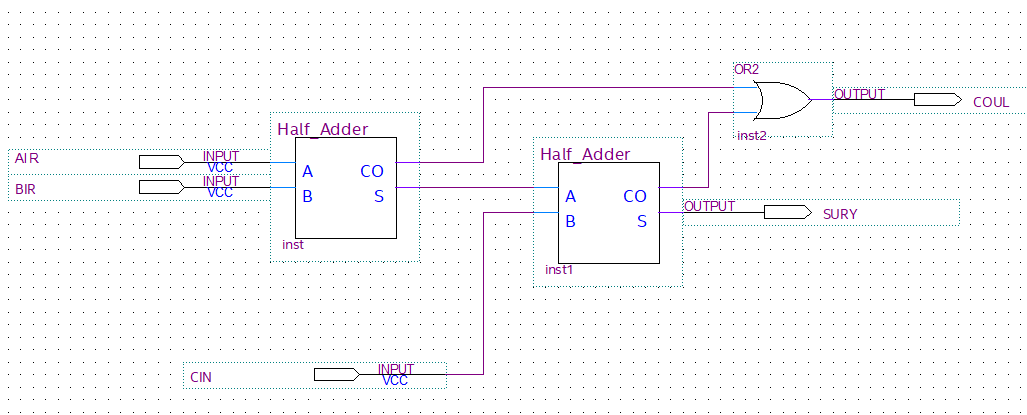

二、设计全加器

1. 新建原理图

-

新建原理图文件,奖上一步保存的半加器元件直接调用

(同样需要生成可调用的元件,为后面的步骤做准备)

- 编译,然后设置为顶层文件

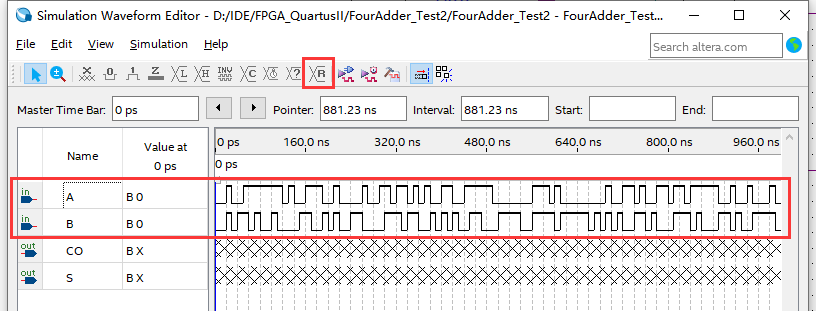

2. 新建波形文件然后仿真

三、硬件部分

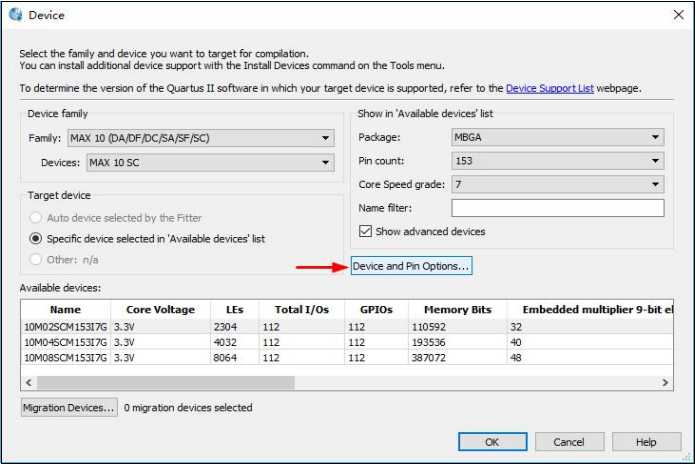

1. 绑定引脚

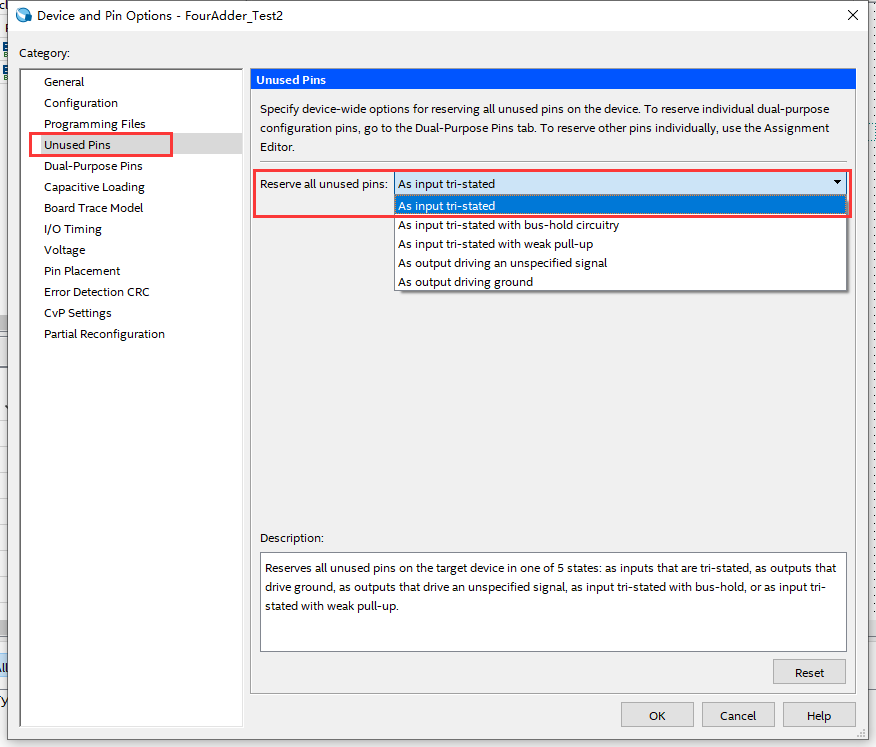

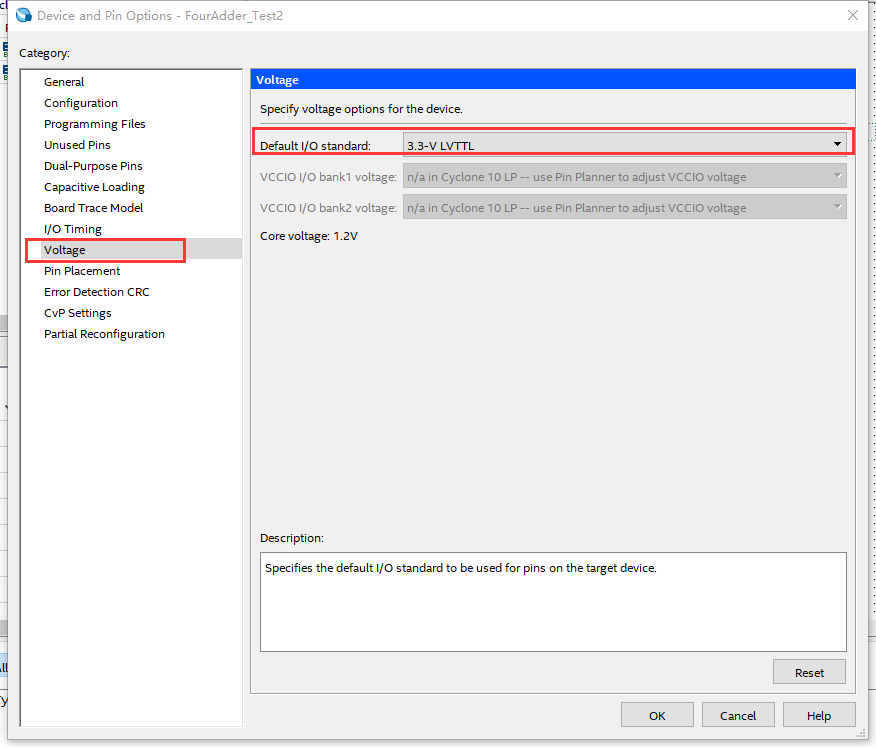

- 选择 Assignments→Device 打开器件配置页面,然后点击页面中的 Device and Pin Options… 选项打开器件和管脚选项页面。

- 在 Unused Pins 选项中配置 Reserve all unused pins 为 As input tri-stated 状态。

- 在 Voltage 选项中配置 Default I/O standard 为 3.3-V LVTTL 状态。然后 OK 回到设计界面。

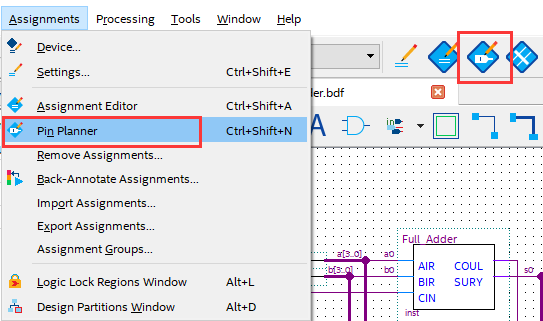

- 选择菜单栏中 Assignments→Pin planner 选项 或 工具栏中 Pin planner 图标,进入管脚分

配界面。

- 在 Pin Planner 页面中将所有端口分配对应的 FPGA 管脚,如下图,然后关闭(自动保存)。

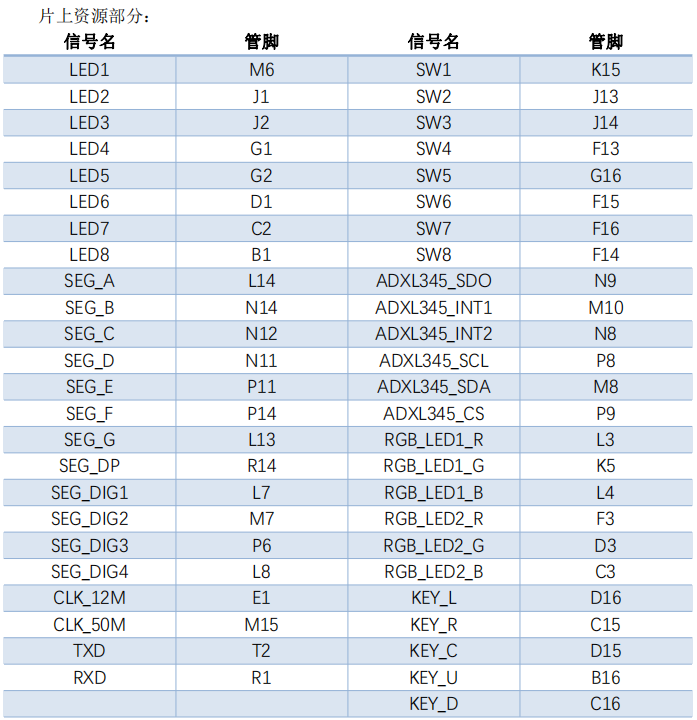

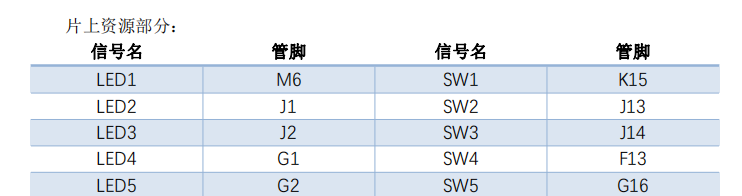

根据参考书中LED1-2,SW1-3的管脚名进行分配:将ABC三个输入端分别分配给SW1-3,两个输出端分别分配给LED1-2,LED亮则为0,不亮则为1

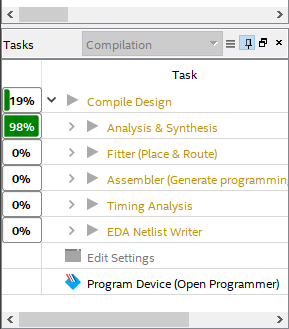

- 选择菜单栏中 Processing→Start Compilation 选项 或 工具栏中 Start Compilation 按钮,开STEP-CYC10 软件手册,开始所有编译,等待 Tasks 列表中所有选项完成,如下图。

2. 下载

-

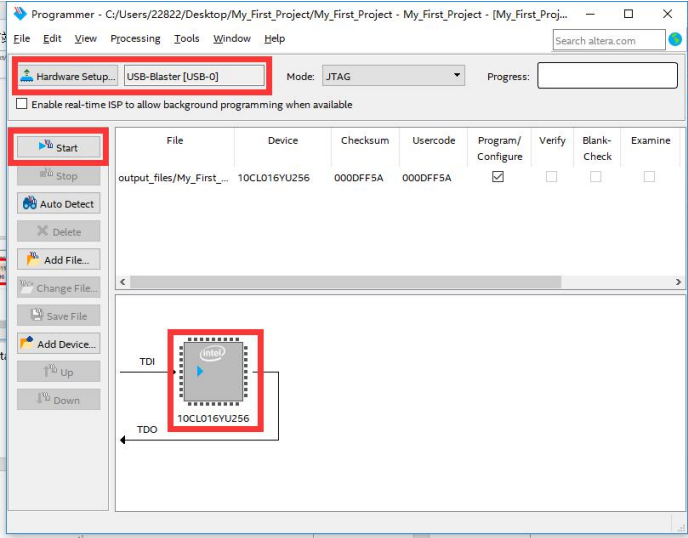

使用 micro-usb 线将 STEP-MAX10 二代开发平台连接至电脑 USB 接口,选择菜单栏中 Tools →Programmer 选项 或 工具栏中 Programmer 按钮,进入烧录界面。

-

烧录界面如下,确认硬件驱动为 USB-Blaster[USB-0],选择 Add File 添加工程输出文件中 sof 格式文件,勾选 Program 列和 Verify 列,点击 Start 按钮进行 FPGA 加载。

-

FPGA 加载完成,界面中 Progress 状态显示 100%(Successful)。观察开发板现象。

3. 测试

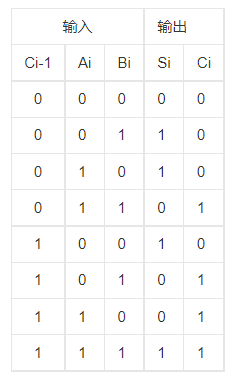

- 全加器真值表:

-

实际效果:

实际测试结果与真值表一一对应,证明电路设计图没有问题

注意:小脚丫的LED亮则为0,灭则为1

四、总结

通过这次实验,我学会了利用 Quartus I 的原理图输入方法设计简单组合电路。

五、参考文章

《实验一:1位全加器设计—— 原理图与VHDL设计初步》

《STEP-CYC10 硬件手册》

《STEP-CYC10 软件手册》

STEP 10资源参考: