在了解了FPGA的基本开发流程之后开始了第一个FPGA实验了,当然和单片机的学习一般,第一天是点灯,主要还是熟悉下FPGA的设计流程。

实验目的是使LED灯500ms亮,500ms灭,最核心的当然就是设计计数器了,在设计计数器的过程之中视频的作者强调我们要摒弃学习单片机的路子,我们不在是配置一个个的寄存器而且建立一个个的电路模型。

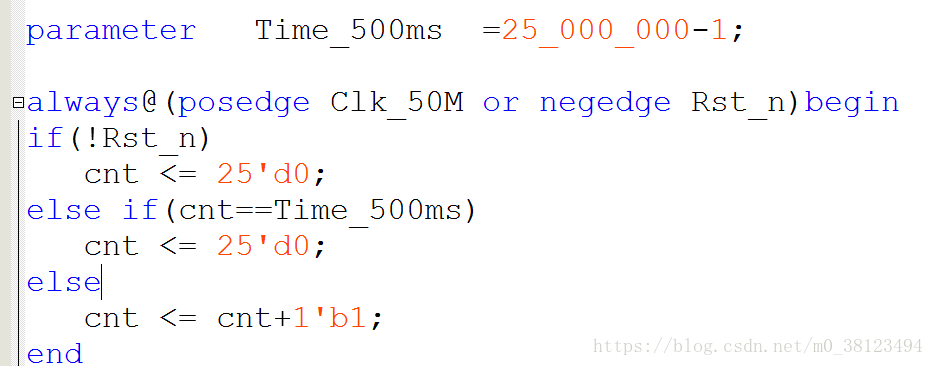

设计计数器计数器注意要点:

1、我们要注意我们每次是从0开始计数的,所以我们要目标值小一位。我们这里晶振是50MHZ的,也就是说每一个周期是20ns,我们要计数到500ms意味着我们要计数500_000_000/20 =25_000_000下,但是我们是从0开始计数的,所以计数到24_999_999就是计数到了25_000_000下。如下图:

2.在进行always块设计的时候我们一个always块中只设计一个信号

always@(posedge Clk_50M or negedge Rst_n)begin

if(!Rst_n)

cnt <= 25'd0;

else if(cnt==Time_500ms)

cnt <= 25'd0;

else

cnt <= cnt+1'b1;

end

always@(posedge Clk_50M or negedge Rst_n)begin

if(!Rst_n)

Led <= 0;

else if(cnt==Time_500ms)

Led <= ~Led;

else

Led <= Led;

end

上面就是将两个信号使用两个always块进行设计。

在确认分析和综合无误之后我们开始进行仿真测试,观察是否和我们预设的功能一样。这里仿真主要分为功能仿真(前仿真)和时序仿真(后仿真),在进行仿真之前我们首先进行激励文件的编写。

`timescale 1ns/1ns //这里相当于时间的基准单位

在激励文件中我们将输入信号设计为reg类型,输出信号设计为wire型(这里本人还不理解,如果有人知道请指出来)

reg clk;

reg rst_n;

wire led;

然后就是对模块进行例化(就是把激励信号和模块的信号进行连接)

counter u1(

.Clk_50M(clk),

.Rst_n(rst_n),

.Led(led)

);

这是时序电路所以我们最主要就是编写时钟信号的激烈

这里使用always #(`clock_period/2) clk=~clk;

这里的clock_period 来自于`define clock_period 20的定义,采用这种定义的方法方便我们进行修改。

我们需要对信号进行激励的赋值。查阅网上的资料,他们说一般情况下initial块只执行一次,我们使用initial块给信号赋值,使用always块给需要多次赋值的信号进行赋值

initial begin

clk =1;

rst_n=0;

#(`clock_period*200);

rst_n=1;

#2000_000_000;

$stop;

end

always #(`clock_period/2) clk=~clk;

这里使用$stop终止仿真。