注:几篇关于 CMOS 的文章合辑,未整理。

数字电子技术基础:门电路(CMOS)

QNee 于 2020-08-12 23:28:31 发布

CMOS

CMOS 是 Complementary Metal Oxide Semiconductor(互补金属氧化物半导体)的缩写。

首先说说 CMOS 是什么?

网络论坛上已经吵翻天了,很多人直接认为 CMOS 就是 MOS 对管,也有人认为 CMOS 是一种半导体技术,不是指具体的 MOS 对管。

大家如果稍微有点时间的话,可以看看,很有趣。

通常所说的 CMOS 是什么意思?(链接已飙,讨论文本附本文末。)

先看看百度百科对 CMOS 的解释

好吧,模棱两可,中庸之道。

再看看维基百科

is a fabrication process,是一种设计工艺)

好吧,也是技术(工艺),我认为都可以,完全看自己怎么理解了。

CMOS(互补金属氧化物半导体)工艺技术被广泛应用于微处理器、微控制器、静态随机存取存储器(SRAM)以及其他各类数字逻辑电路的制造。此外,该技术亦被用于模拟电路的设计与实现,其中许多现代图像传感器均基于CMOS工艺技术构建。

在 CMOS 电路中,以及集成电路中,MOS 管都是很重要的元件,是构成电路的基本元件。而 CMOS 电路中的基本单元是 MOS 对管,就是使用 P 沟道和 N 沟道 MOS 对接的一种电路。

具体电路如下(这也是 CMOS 反相器的电路)

MOS 管

MOS 管分为:N 沟道增强型、P 沟道增强型、N 沟道耗尽型、P 沟道耗尽型。

g:栅极

d:漏极

s:源极

上图是 N 沟道增强型 MOS 管,工作原理如下:

1、当栅极和源极两端不加电压,Vgs = 0,漏极和源极之间只是两只背向的 PN 结,不存在导电沟道,因此即使漏极和源极两端之间加电压,Vds != 0,也不会有漏极电流。

2、当 Vds = 0,且 Vgs > 0 时,由于绝缘层存在,栅极电流为 0。但是栅极金属层将聚集正电荷,他们排斥 P 型衬底靠近绝缘层一侧的空穴,使之剩下的不能移动的负离子区,形成耗尽层,如下图:

当 Vgs 增大时,一方面耗尽层增宽,另一方面将衬底的自由电子吸引到耗尽层和绝缘层之间,形成一个 N 型薄层(反型层),这个反型层就构成了漏极和源极之间的导电沟道。

使沟道刚刚形成的 Vgs 为开启电压,Vgs 越大,反型层越大,导电沟道电阻越小。

1、CMOS 反相器(非门)

其中 T1 为 P 沟道增强型 MOS 管,其中 T2 为 N 沟道增强型 MOS 管

2、CMOS 与非 / 或非门

3、漏极开路输出门电路(OD 门)

OD 门输出电路是一个漏极开路的 N 沟道增强型 MOS 管 TN

OD 门符号中,菱形下方的横线表示输出低电平时为低输出电阻

OD 门工作时,必须将输出端经上拉电阻接到电源上,而两个 OD 门可以构成线与电路

4、CMOS 传输门

CMOS 传输门用于将电压取倒数

5、CMOS 异或门

6、CMOS 三态输出门电路(输出缓冲器)

其中,逻辑符号中 ,EN’连接的○代表低电平有效

EN = 0 时,Y = A’;

EN = 1 时,Y = Z(高阻态)(X 代表不定态)

注:以上图片大多截取自《数字电子技术基础(阎石)》和《模拟电子技术基础》

-

数字电子技术基础(四):门电路(CMOS)必看_cmos 异或门电路 - CSDN 博客

数字电路基础知识 ——CMOS 门电路 (与非门、或非、非门、OD 门、传输门、三态门)

摆渡沧桑 于 2019-09-01 20:51:59 发布

数字电路基础知识 ——CMOS 门电路 (非门、或非门、与非门、或门、与门、与或非门、异或门、OD 门、传输门、三态门)

先了解二极管门电路逻辑,再次介绍 CMOS 门电路,也是 IC 中用的最广泛的门电路。

主要了解与非门、或非门以及相同面积的 cmos与非门和或非门哪个更快。OD 门、传输门、三态门。

一、二极管门电路

CMOS 门电路介绍之前,先介绍二极管门电路:

1.与门

只要有一个为低电平,Y 端就被拉低到 0.7V

2.或门

只要有一个为高电平,Y 端就被拉高到 2.3V

3.二极管门电路的缺点

输出的高低电平数值和输入的高低电平不相等,相差一个导通电压,如果输出作为下一级门输入信号,将发生高、低电平偏移

输出端对地接上负载电阻,组在电阻的改变会影响输出高电平。因此,这种电路只用作 IC 内部的逻辑单元,并不能作为输出端直接驱动负载。

二、CMOS 门电路

1.反相器(非门)

数字电路基础知识——反相器的相关知识(噪声容限、VTC、转换时间、速度的影响因素、传播延时等)

摆渡沧桑 于 2019-08-27 16:48:38 发布

数字电路基础知识——反相器的相关知识(噪声容限、VTC、转换时间、速度的影响因素、延时等)

反相器是数字电路中最基本的门电路之一,由NMOS和PMOS组成。学过半导体器件的都对此结构比较清楚。

下面我总结了一些反相器相关的知识:

一、反相器的结构

反向器由NMOS和PMOS组成,栅端(G)相连作为输入端,漏断相连作为输出端,NMOS的源端接地,PMOS的源端接电源VDD.

二、反相器的电压、电流传输特性

AB:T1导通T2截止

BC:T1T2导通

CD:T1截止T2导通

VTC(Voltage Transfer Characteristics)曲线:

VTC的形状基本上与高于阈值的操作相同。VTC陡峭部分的斜率取决于反向器的亚阈值斜率。

其中涉及到的的四个重要参数:

VIH:输入电压由高到低变化时,输出电压开始上升且传输特性曲线斜率为-1的点,即图中B点对应的输入电压。(仍能维持输出为逻辑 “0” 的最小输入电压)

VIL:输入电压由低到高变化时,输出电压开始下降且传输特性曲线斜率为-1的点,即图中A点对应的输入电压。(仍能维持输出为逻辑 “1” 的最大输入电压)

VOH:定义为最小合格高电平。(维持输出为逻辑“1”的最小输出电压)

VOL:定义为最大合格低电平。(维持输出为逻辑“0”的最大输出电压)

CMOS集成电路内部规定Vol = 0v,Voh = Vdd。

三、反相器的噪声容限(VTC曲线)

噪声容限定义:

输入为高电平的噪声容限:VNH=VOH-VIH

输入为低电平的噪声容限:VNH=VIL-VOL

四、反相器的亚稳态

当反相器输入电压(Vil+Vih)/2接近于0.5Vdd,CMOS反相器的阈值电压也接近于0.5Vdd,这样输出不确定会是高电平还是低电平,输出呈亚稳态!

对于下面如下首尾相连的反向器结构:

图中的SNN即为静态噪声容限,方框面积越大,表示容限越大。

并且此电路只能工作在三种状态,分别是三个交点,当状态不在这三种状态时,输入、输出会将他们拉向两端。

五、反相器的动态特性

1)先解释两个名词:

- Transition Time(转换时间):

上升时间tr:从10%Vdd上升到90%Vdd的时间,

下降时间tf:从90%Vdd下降到10%dd的时间。

上升时间和下降时间统称为Transition Time,也有定义为20%到80%。

- Propagation Delay(传播延时):

在输入信号变化到 50%Vdd到输出信号变化到50%Vdd之间的时间。

2)动态功耗

反相器从一种稳定状态突然变到另一种稳定状态的过程中,将产生附加的功耗,即动态功耗。

动态功耗包括:负载电容充放电所消耗的功率Pc和PMOS、NMOS同时导通所消耗的瞬时导通功耗PT

在工作频率较高的情况下,CMOS反相器的动态功耗要比静态功耗大得多,静态功耗可以忽略不计。

- 导通功耗PT:

- 负载电容充放电功耗Pc

总功耗为P=PT+Pc

六、扇入(fan-in)和扇出(fan-out)

-

扇入:是指直接调用该模块的上级模块的个数。扇入大表示模块的复用程序高。

-

扇出:是指该模块直接调用的下级模块的个数。扇出大表示模块的逻辑复杂度高,需要控制和协调过多的下级模块;

对于一定扇出数的电路,电路的工作频率随之确定,一般工作频率越高,扇出数越小。在低频(< 1MHz)的工作条件下,CMOS电路的扇出数可以达到50以上。

因此。扇入越大越好,扇出越大越坏。在设计中,尽量减小扇出

2. 常用的逻辑门:或非门、与非门

除了反相器,比较常用的有 或非门、与非门、或门、与门、与或非门、异或门等。

逻辑表达式分别为:

**Y=(AB)’

T=(A+B)’

下面主要了解下与非门其缺点、和改进的电路.

主要缺点:

1)输出电阻 R0 受输入状态影响,即输出电阻不一样,能够相差四倍。如:

A=1, B=1,则 R0 = Ron2 + Ron4 = 2Ron

A=0, B=0,则 R0 = Ron2 // Ron4 = 1/2Ron

A=0, B=1,则 R0 = Ron1 = Ron

A=0, B=0,则 R0 = Ron3 = Ron

2)输出的高低电平受输入端数目的影响

输入端越多,,串联的驱动管数目也越多,输出的 VOL 越高,VOH 也更高。

当输入端全部为低电平时,输入端越多负载并联的数目越多,输出的高电平 VOH 也越高。

3)使 T2、T4 的 Vgs 达到开启电压时,对应的 Vi 也会不同

相同面积的 cmos 与非门和或非门哪个更快 —— 与非门会更优

学过半导体器件都知道,电子迁移率是空穴的 2.5 倍(在硅基 CMOS 工艺中),运算就是用这些大大小小的 MOS 管驱动后一级的负载电容,翻转速度和负载大小一级前级驱动能力相关。为了上升延迟和下降延迟相同,PMOS 需要做成 NMOS 两倍多大小。

载流子的迁移率,对 PMOS 而言,载流子是空穴;对 NMOS 而言,载流子是电子。

PMOS 采用空穴导电,NMOS 采用电子导电,由于 PMOS 的载流子的迁移率比 NMOS 的迁移率小,所以,同样尺寸条件下,PMOS 的充电时间要大于 NMOS 的充电时间长。

在互补 CMOS 电路中,与非门是 PMOS 管并联,NMOS 管串联,而或非门正好相反,所以,同样尺寸条件下,与非门的速度快,所以,在互补 CMOS 电路中,优先选择与非门。

针对上面问题进行改进

采用或非门加反相器(缓冲器就是与非门,如上图所示。

带缓冲的门电路,输出电阻、输出的高低电平以及电压传输特性将不受输入端状态的影响

对于或非门,则是与非门加缓冲器。

3.OD 门(漏极开路的门电路)

OD 门:为了满足输出电平的转换,吸收大负载电流以及线与逻辑,将 MOS 改为漏极开路

OD 输出的与非门结构图如下:

OD 门工作必须接上拉电阻 RL 到电源上。

OD 门的应用:可以将多个 OD 门输出端直接相连,实现线与逻辑,即将输出并联使用,可以实现线与或用作电平转换和驱动。如下图所示:

Y1、Y2 中任何一个为低电平,输出都为低电平,同时为高时,输出才为高电平。

4.传输门

CMOS 传输门:利用 P 沟道 MOS 管和 N 沟道 MOS 管互补的特性连接如下图

T1 是 N 沟道增强型 MOS 管,T2 是 P 沟道增强型 MOS 管。T1 和 T2 的源极和漏极分别相连作为传输门的输入端和输出端。C 和 C’是互补的控制信号。

由于 CMOS 传输门的结构是对称的,所以,输出端和输入端可以互换,是一个双向器件。

CMOS 传输门的应用:

1)传输门和反相器构成异或门电路:

A=1,B=0,TG1 截止,TG2 导通,Y=B’=1

A=0,B=1,TG1 导通,TG2 截止,Y=B=1

A=0,B=0,TG1 导通,TG2 截止,Y=B=0

A=1,B=1,TG1 截止,TG2 导通,Y=B‘=0

2)模拟开关:

由传输门和一个反相器组成,双向器件。

传输连续变化的模拟电压信号。

5.三态门

1)高阻态:

三态门除了高低电平,还有第三个状态 —— 高阻态。

高阻态:电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

三态门常用在 IC 的输出端,也称为输出缓冲器

2)下图是 CMOS 三态输出反相器的结构:

当 EN’=0 时,Y=A’:

A=1,G4、G5 的输出为高电平,T1 截止、T2 导通,Y=0;

A=0,G4、G5 的输出为低电平,T1 导通、T2 截止,Y=1;

当 EN’=1 时,不管 A 为高低状态,G4 输出高电平,G5 输出低电平,T1 和 T2 同时截止,输出呈现高阻态。

3)三态门的应用:

减少各单元之间的连线数目:

数据的双向传输:

4)还有几种常见的三门结构:

图一:

三态非门,当~EN 为 1 时,最上面的 PMOS 和最下面的 NMOS 管截止,无论 A 取什么状态,输出为高阻态,反之输出为Y= ~ A

图二:

利用一个与非门,得到三态缓冲门,当~EN 为高电平时,最上面的 PMOS 管截止,输出为高阻态,反之,输出为Y=A

图三:

三态非门,在反相器后面加一个传输门,当~EN 为低电平,传输门导通,输出Y = ~A,反之传输门截止,输出高阻态。如果想要 EN 高电平有效,交换传输门上下端子的反相器即可。

图四:

利用一个与非门,得到三态缓冲门,当~EN 为高电平时,最上面的 PMOS 管截止,输出为高阻态,反之,输出为Y=A

via:

-

数字电路基础知识 ——CMOS 门电路 (与非门、或非、非门、OD 门、传输门、三态门)_cmos 异或门 - CSDN 博客

-

数字电路基础知识——反相器的相关知识(噪声容限、VTC、转换时间、速度的影响因素、传播延时等)-CSDN博客

数字电路基础(CMOS 电路、低功耗方法)

SD.ZHAI 已于 2022-05-13 15:37:12 修改

一、CMOS 器件

1.1.CMOS 反相器

CMOS 反相器实现非门功能,由一个 P MOS 管 和一个 NMOS 管组成,其逻辑电路图如下:

补充:当将一个 PMOS 管和一个 NMOS 管并联,则会组成一个传输门(TG)电路。

其真值表如下:

当然,以下是格式化后的 Markdown 表格:

| In | PMOS | NMOS | Out |

|---|---|---|---|

| 0 | √ 导通 | × 关闭 | 1 |

| 1 | × 关闭 | √导通 | 0(接地) |

在实际制造过程中,PMOS 管比 NMOS 管要宽,这是由于 PMOS 管是由空穴导电,NMOS 管由电子导电,而电子迁移率要比空穴迁移率高得多(约 2 倍)造成的。

1.2.CMOS 与非门

CMOS 与非门由两个并联的 PMOS 管,2 个串联的 NMOS 管组成的。

其真值表如下:

| A | B | PMOS(A) | PMOS(B) | NMOS(A) | NMOS(B) | Out |

|---|---|---|---|---|---|---|

| 0 | 0 | √ 导通 | √ 导通 | × 关闭 | × 关闭 | 1 |

| 0 | 1 | √ 导通 | × 关闭 | × 关闭 | √ 导通 | 1 |

| 1 | 0 | × 关闭 | √ 导通 | √ 导通 | × 关闭 | 1 |

| 1 | 1 | × 关闭 | × 关闭 | √ 导通 | √ 导通 | 0(接地) |

1.3.CMOS 或非门

CMOS 或非门由两个串联的 PMOS 管,2 个并联的 NMOS 管组成的。

其真值表如下:

| A | B | NMOS(A) | NMOS(B) | PMOS(A) | PMOS(B) | Out |

|---|---|---|---|---|---|---|

| 0 | 0 | × 关闭 | × 关闭 | √ 导通 | √ 导通 | 1 |

| 0 | 1 | × 关闭 | √ 导通 | √ 导通 | × 关闭 | 0(接地) |

| 1 | 0 | √ 导通 | × 关闭 | × 关闭 | √ 导通 | 0(接地) |

| 1 | 1 | √ 导通 | √ 导通 | × 关闭 | × 关闭 | 0(接地) |

1.4 CMOS 与门和 CMOS 或门

分别将 CMOS 与非门、CMOS 或非门的 VDD 端和接地端互换即可,可由真值表进行验证,此处不再给出具体 CMOS 电路图。

1.5 CMOS 电路重要技术参数

- 输入和输出的高、低电平;

输入低电平的上限值 VIL(max)

输入高电平的下限值 VIH(mix)

输出低电平的上限值 VOL(max)

输出高电平的下限值 VOH(mix)

- 噪声容限—— 门电路的抗干扰能力,电路的噪声容限越大,抗干扰能力越强。

输入高电平的噪声容限:VNH = VOH(mix) - VIH(mix)(输出 - 输入)

输入低电平的噪声容限:VNL = VIL(max) - VOL(max)(输入 - 输出)

-

传输延迟时间—— 表征门电路开关速度的参数,其值与电源电压 VDD 和负载电容有关。

-

功耗—— 分为静态功耗和动态功耗两部分。

-

延时 — 功耗积—— 衡量电路的综合性能指标(较快的工作速度、较低的功耗)

-

扇入与扇出数—— 表征门电路的输入端信号个数和输出端信号个数。

二、CMOS 电路 —— 功耗

CMOS 电路功耗需要考虑两个部分:静态功耗、动态功耗;其中静态功耗是指电路输出没有动态转换时的功耗,动态功耗是指电路发生状态转换时的功耗,动态功耗主要包括两个部分,一是指电路输出状态转换瞬间 MOS 管的导通功耗,二是指电路输出由高电平转为低电平,或者由低电平转为高电平时对电容(CMOS 管的负载是电容性的)进行充放放电的过程,增加的电路损耗。

总功耗 = 静态功耗 + 开关功耗 + 短路功耗

动态功耗由开关功耗(翻转功耗)和短路功耗两个部分组成。

开关功耗 = CV2F C 为负载电容,V 是电压,F 是频率

短路功耗 = V I(短路) I(短路)为开关在切换过程中 N 极和 P 极同时有效地短路电流

静态功耗 = V I(漏电) 静态功耗(又称漏电功耗)是晶体管在电路稳定时出现漏电造成的功耗。

需要注意的是,升高电压可以提高电路性能,但也会增加功耗;温度升高也会使功耗增加。那在电路设计中,如何有效降低功耗呢?

可通过做时钟门控(clock gating),降低翻转率,即降低频率的方式来降低电路功耗;此外还可以通过降低电压的方式,诸如 DVFS(动态电压频率调整),多阈值电压技术,多电压技术等来有效降低功耗

2.1. 时钟门控

时钟门控(clock gating):在数据无效时,将寄存器时钟关闭的技术,能够有效降低功耗, 是低功耗设计的重要方法之一。门控时钟其实就是一个逻辑模块,在寄存器的输入数据无效时,将寄存器的输入时钟置为 0,而此时寄存器值保持不变,此时没有时钟翻转,避免了动态功耗。

1)、不含锁存器的时钟门控电路

这种系统时钟门控的机制算然简单,但是使能信号周期的不确定,会使时钟过早的被截断或者产生时钟毛刺。为了产生正确的时钟信号,要求使能信号从时钟上升沿到时钟下降沿保证稳定的常量。

2)、含有锁存器的时钟门控电路

含有锁存器的时钟门控电路,借助于锁存器,使得时钟信号在高电平期间或在低电平期间保证稳定的值,不发生翻转。生成时钟门控的 RTL 代码如下:

推荐的风格代码,else 分支忽略,此时意味着在 data_vld 无效时 data_out 保持不变,此时状态相当于将寄存器输入时钟 CLOCK 置为 0,只是没有翻转,因此降低了动态功耗;而不推荐风格代码,在 data_vld 无效时 data_out 为 0,会发生时钟翻转,不符合门控时钟的状态,无法生成门控时钟。

上图两个电路图均为推荐风格代码的映射电路图,右侧为采用门控时钟设计的电路图。采用推荐风格代码的代码即可以通过 EDA 工具自行插入门控时钟。

2.2. 动态电压频率调整 DVFS

DVFS(Dynamic Voltage and Frequency Scaling)动态电压频率调节本质上是一种自适应的电压频率调节技术,也是一种低功耗技术,目的是根据的芯片当时的实际功耗需要设定工作电压和时钟频率,这样可以保证提供的功率既满足要求又不会性能过剩,从而可以降低功耗。

一味的降频降压当然是不能降低功耗的,因为低频下运行可能使系统处理任务的时长增加,从而整体上可能增加了功耗。所以 DVFS 的核心是动态调整的策略,其目的是根据当时的系统负载实时调整,从而提供满足当时性能要求的最低功率,也就达到了最低功耗。基本的策略当然是工作负载增加时先升压再升频,工作负载降低先降频在降压。

比如使用该技术可以动态调节 CPU 工作频率和工作电压,如当 CPU 高速工作时候,选择合适电压供应给 CPU; 当 CPU 处于空闲或者睡眠状态时,系统会自动切换到合适的低电压以达到降低系统功耗的目的。

2.3. 多阈值电压技术

器件的栅电压定义为阈值电压,它是 MOSFET 的重要参数之一。因为不同阈(yu)值电压 Vth 对应的器件其漏电流 Leakage 差异很大,且漏电流随着阈值电压 Vt 的增加而指数下降,如下图所示,

我们可以通过在不同的时序路径上使用不同阈值电压的标准单元来降低漏电流,已达到降低漏电功耗的目的。

-

低阈值电压标准单元:速度快、泄漏功耗高;

-

高阈值电压标准单元:速度慢、泄漏功耗低。

2.4. 多电源多电压技术

多电源多电压(MSMV)是一种可以有效降低动态功耗的技术,简称多电压技术。所谓多电源,是指不同逻辑模块处于不同的电源域中,由不同供电电源供电。

具体而言,在芯片设计时候,对于工作频率要求高的系统或者模块使用高电压,对于工作频率要求不高的系统或者模块使用相应的低电压也称 Normal 电压,从而实现低功耗的目的。

比如手机基带芯片中的 CPU 或者 GPU 系统模块要在高电压状态下才能才能达到系统工作要求。而对于一般的只要求能够达到普通性能的模块则可以用较低的电压进行供给,比如系统中需要一直上电的 Always-ON 区域中的 Timer 计时器等等。

除了上述的降低功耗技术外,还有许多其他的降低功耗的技术。

https://blog.csdn.net/DdiIcey/article/details/78545481

via:

-

数字电路基础(CMOS 电路、低功耗方法)_tg 门逻辑真值表 - CSDN 博客

https://blog.csdn.net/weixin_46022434/article/details/105273355

电子技术 ——CMOS 逻辑门电路

爱寂寞的时光 已于 2023-03-04 12:25:27 修改

在本节我们介绍如何使用 CMOS 电路实现组合逻辑函数。在组合电路中,电路是瞬时发生的,也就是电路的输出之和当前的输入有关,并且电路是无记忆的也没有反馈。组合电路被大量的使用在当今的数字逻辑系统中。

晶体管的开关模型

CMOS 数字电路使用 NMOS 和 PMOS 晶体管作为开关使用。之前,我们知道,MOS 可以工作在三极管区(相当于开关闭合),也可工作在截止区(相当于开关断开)。

特别的,当一个 NMOS 作为闭合的开关的时候,此时栅极电压处于高电压,相当于一个从漏极到源极直接相当小的一个电阻 R o n R_{on} Ron或 r D S r_{DS} rDS,通常处在高电压 V D D V_{DD} VDD状态,表示逻辑 1。相反,当栅极为低电压的时候,此时 MOS 截止,表示逻辑 0,没有电流流过 MOS,如图:

而 PMOS 则工作在相反的状态,栅极高电压,MOS 管截止,栅极低电压,MOS 管导通,如图:

我们观察到 MOS 管的栅极通常是逻辑控制输入节点,通常作为逻辑门的输入端。

CMOS 反相器

在了解 MOS 开关的工作方式之后,先让我们制作一个反相器。正如其名,反相器可以逆转输入的逻辑,即输入 0 输出 1,反之亦然。因此该功能可以使用布尔函数表示为:

Y = X ‾ Y = \overline {X} Y=X

其抽象电路模型和实现电路如图所示:

它由一对 CMOS 组成,栅极相连,作为输入端 X X X,漏极相连作为输出端 Y Y Y。当 X = 1 X=1 X=1的时候,即 V X = V D D V_X = V_{DD} VX=VDD,此时 PMOS 截止,而 NMOS 导通,输出 Y = 0 Y = 0 Y=0。当 X = 0 X=0 X=0的时候,PMOS 导通而 NMOS 截止,此时输出 Y = 1 Y=1 Y=1。

CMOS 逻辑门的一般结构

由上面的反相器我们能总结出 CMOS 逻辑门的一般结构,反相器由一个 NMOS下拉晶体管和一个 PMOS上拉晶体管组成。CMOS 逻辑门由两个网络组成:一是下拉网络 PDN由 NMOS 组成 ,二是上拉网络 PUN由 PMOS 组成。如图:

这两个网络都受到输入变量的控制,做出相反的行为,上图是一个三变量输入的逻辑门,当输入变量满足 PDN 条件的时候,此时 PDN 网络导通,而 PUN 网络截止,输出 Y = 0 Y=0 Y=0,反之亦然。

因此,我们可以根据不同的 PDN 和 PUN 的实现,来实现与门、或门等一些基本的门电路,下图是一些 PDN 网络的例子:

在图 (a) 我们发现当 A = 1 A=1 A=1的时候, Q A Q_A QA导通此时 Y = 0 Y = 0 Y=0,同样的对于 B = 1 B = 1 B=1, Q B Q_B QB导通此时 Y = 0 Y = 0 Y=0,因此图 (a) 是一个或门的 PDN 实现,可以表示为:

Y ‾ = A + B \overline {Y} = A + B Y=A+B

或是:

Y = A + B ‾ Y = \overline {A + B} Y=A+B

图 (b) 必须两个 NMOS 全部导通才能输出,是一个与门结构,可以表示为:

Y ‾ = A B \overline {Y} = AB Y=AB

或是:

Y = A B ‾ Y = \overline {AB} Y=AB

最后一个例子图 © 是一个组合逻辑,可以表示为:

Y ‾ = A + B C \overline {Y} = A + BC Y=A+BC

或者等效于:

Y = A + B C ‾ Y = \overline {A + BC} Y=A+BC

接下来我们考虑一些 PUN 的一些例子,如图:

图 (a) 当 A = 0 A = 0 A=0 或是 B = 0 B = 0 B=0 的时候输出 Y = 1 Y = 1 Y=1表示为:

Y = A ‾ + B ‾ Y = \overline {A} + \overline {B} Y=A+B

图 (b) 当 A = 0 A=0 A=0 并且 B = 0 B= 0 B=0 的时候导通,表示为:

Y = A ‾ B ‾ Y = \overline {A} \ \overline {B} Y=A B

而图 © 表示为:

Y = A ‾ + B ‾ C ‾ Y = \overline {A} + \overline {B} \ \overline {C} Y=A+B C

在学习完 PDN 和 PUN 理论之后,我们就可以准备搭建我们的门电路了。首先,为了方便,我们不再使用模拟电路中的 MOS 符号,而是使用一种更加方便的数字电路 MOS 表示符号,如图:

上图中左边的符号是模拟 MOS 表示,而右边是数字 MOS 表示,对于 PMOS 我们发现在栅极的地方有一个小圈,这表示当输入是低电压的时候才导通。除此之外,数字 MOS 忽略了漏极栅极之分。

或非门 NOR 电路

首先我们考虑一个 CMOS 的或非门电路:

Y = A + B ‾ = A ‾ B ‾ Y = \overline {A + B} = \overline {A} \ \overline {B} Y=A+B=A B

等式中间给出了 PDN 实现,等式右边给出了 PUN 实现,将两个实现组合在一起,我们得到:

与非门 NAND 电路

与非门电路可以表示为:

Y = A B ‾ = A ‾ + B ‾ Y = \overline {AB} = \overline {A} + \overline {B} Y=AB=A+B

等式中间给出了 PDN 实现,等式右边给出了 PUN 实现,将两个实现组合在一起,我们得到:

一个更复杂的门电路

考虑下面的组合布尔表达式:

Y = A ( B + C D ) ‾ Y = \overline {A (B+CD)} Y=A(B+CD)

因为 PDN 是整体反相,因此可以直接给出 PDN 实现,对于 PUN 则是变量反相,可以通过德・摩根定律展开表达式:

Y = A ‾ + B ‾ ( C ‾ + D ‾ ) Y = \overline {A} + \overline {B}(\overline {C} + \overline {D}) Y=A+B(C+D)

给出实现:

需要注意的是,有时候并不总是可以通过对偶律来获得两个网络的实现。对于以上情况,需要更加复杂的布尔逻辑推导。

异或门 XOR 电路

另一个重要的逻辑电路是异或门电路,表示为:

Y = A B ‾ + A ‾ B Y = A \overline {B} + \overline {A} B Y=AB+AB

我们观察到给出 Y Y Y我们可以先考虑 PUN,但不幸的是,表达式不是由每个变量的反相值构成,因此我们需要额外的反相器,如图的 PUN:

如上图,左边的 A ‾ \overline {A} A和右边的 B ‾ \overline {B} B都需要先反相才能输入到 PUN 中,因此需要额外的两个反相器,对于 PDN,通过对偶变换可以得到:

Y ‾ = A B + A ‾ B ‾ \overline {Y} = AB + \overline {A} \ \overline {B} Y=AB+A B

对应的 PDN 实现为:

同样需要两个额外的反相器。则此异或门电路总共需要 12 个晶体管。

有趣的是,上图中两个 PDN 和 PUN 网络不是对偶网络,实际上,PDN 和 PUN 网络对偶并不是必要条件。

总结

-

PDN 网络可以通过关于非互补变量的 Y ‾ \overline {Y} Y的表达式得到,若表达式中存在互补变量,需要额外的输入反相器。

-

PUN 网络可以通过关于互补变量的 Y Y Y的表达式得到,若表达式中存在非互补变量,需要额外的输入反相器。

-

PDN 网络可以将 PUD 网络进行对偶得到,反之亦然。

via:

-

电子技术 ——CMOS 逻辑门电路_cmos 门电路 - CSDN 博客

https://blog.csdn.net/jiahonghao2002/article/details/129297859

CMOS 工艺下的 BJT 你了解多少?

jf_78858299・来源:日芯说・作者:日芯说・2023-02-02 14:00

有没有同学好奇,作为模拟芯片设计师,几乎都在用 CMOS 工艺,大部分电路也是用的 MOSFET,很少用 BJT 去设计大规模电路,那么,到底应该对 BJT 这种 device 掌握到什么 level 呢?

其实我也不能下定论,我就说说我的掌握程度吧。

当然 BJT 基本的工作原理肯定要掌握的。

本文谈一谈 BJT 这个 device、以及模拟 IC 设计师眼中对 BJT 的了解程度(只用过 CMOS 工艺的模拟 IC 设计师)。

BJT 即三极管,分为 PNP 和 NPN 型,简单示意图如下图所示。

NPN 和 PNP

以 NPN 为例,其剖面图如下图,PNP 的剖面图想必你肯定也知道了。

NPN 的剖面图

说到这里,大家是不是好奇,具体到某一种工艺中,BJT 的剖面图会是什么样子的?

读研三年和工作几个月,我只用过一种工艺,那就是大家都知道的 CMOS 工艺。

其实,“正宗” 的 BJT 应该是用 Bipolar 工艺制造的。但是现实用这种工艺不多,很多年前,确实会用这种工艺,由于 Bipolar 工艺 process 繁多,价格也比 CMOS 工艺贵,集成度也远输于 CMOS,慢慢大家都不怎么用 Bipolar 工艺了。

在 CMOS 工艺中,BJT 的制作和 Bipolar 不同,可以说,CMOS 工艺中,不是 “正宗” 的 BJT device,而是一种寄生的 BJT。

不知道有没有认真的同学发现,你所用的单纯的 CMOS 工艺中,只有 PNP 的 BJT 而没有 NPN 的 BJT?

在没有 DNW 的 CMOS 工艺中,的确如此,且一般是纵向的寄生 PNP 三极管。why?

因为,没有 DNW 的工艺中,只有全局 P-sub 是和 P + 是 P 型半导体,这里 P-sub 充当 PNP 的一个 “P”,即集电极,P + 充当 PNP 的另一个 “P”,即发射极,n-well 充当 PNP 的 “N”,即基极,而不是 Bipolar 工艺真正意义上的 N 和 P。

PS:至于为什么是纵向的而不是横向的 PNP,原因作者也布吉岛啦。

这里,全局 P-sub 衬底永远接 VSS。

CMOS 工艺中的纵向寄生 PNP

看到这里,知道为什么普通 CMOS 工艺没有 NPN 了吗?

NPN 正常工作的时候,基极发射极电压 Vbe 应大于其开启电压,也就是说基极电位大于 0,但是 CMOS 工艺中 p-sub 永远是 VSS 不可能大于 0,因此 p-sub 是不能做 NPN 的基极的。

有同学会问了,能不能用两个 n-well 做 NPN 的两个 “N”,用 P + 做 NPN 的 “P” 呢?

答案是不能。why?n-well 外面的 P + 就是衬底接触,也是接 VSS 的。

这里,建议有兴趣的同学可以仔细画一画这些寄生 BJT 的剖面图,结合 CMOS 工艺的特点进行分析,牢记 BJT 中遵循发射结正偏,集电结反偏的原理,看看在 CMOS 工艺中能否实现。

那么 CMOS 工艺中,就不能有 PNP device 了吗?肯定不是。

在有 DNW 的 CMOS 工艺中或者有双 P-well 的 CMOS 中,是可以有寄生的 NPN 的。

在 DNW 工艺中,DNW 本身就是用来制造隔离的 NMOS,DNW 的存在使得 NMOS 的 P 衬底是” 本地 “的,即可以不接到全局 p-sub 上,因此就有了 NPN 中的基极 “P”。

而在拥有双 P-well 的 CMOS 的工艺中,多出来的 P-well 充当 NPN 的基极 “P”,如下图:

浅阱 NPN 的剖面图

但是,双 P-well,相比传统 CMOS,多了一层浅 P 阱 mask,增加了成本。

在 CMOS 工艺中,纵向寄生 PNP 的 β 值不会很大,一般不会超过 10,具体数据可查看 PDK 中关于 Bipolar 的拟合数据。为什么 β 很小,我们知道,基区的厚度越大,β 越小。在 CMOS 工艺中,也就是 n-well 的厚度,是较大的,因此 β 会很小,然而这个厚度是我们 designer 不可控的,是由 foundry 决定的。

到现在为止,作为模拟 IC 设计师,我只在 bandgap 中用过 BJT,而且用的也不是其对基极电流的放大作用,而是两个 BJT 的 Vbe 差值与温度成正比这个特性,如下图。

PTAT 电压产生电路

mentor 说,在 ESD 电路中,基本都是二极管和 MOS,BJT 几乎不用。

因此,到现在为止,我对 BJT 的了解可以说很少,不多,但知道 BJT 的工作原理,足够在 CMOS 工艺中进行 电路设计,毕竟 latch up 效应或者 ESD 中的 GGNMOS 和 GGPMOS 用到的寄生 BJT 的特性。

-

CMOS工艺下的BJT你了解多少?-电子发烧友网

BJT 与 MOSFET 与 IGBT 的区别

破风浪挂云帆 于 2017-06-19 14:50:37 发布

一.MOSFET 与 IGBT 的区别

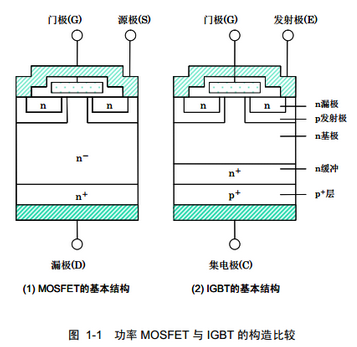

从结构上来讲,以 N 型沟道为例,IGBT 与 MOSFET 的区别在于 MOSFET 的衬底为 N 型,IGBT 的衬底为 P 型;从原理上说 IGBT 相当于一格 MOSFET 与 BIpolar 的组合,通过背面 P 型层空穴降低器件的导通电阻,但同时也会引入一些拖尾电流问题,从产品上来说,IGBT 一般用在高压功率产品上,从 600V 到几千伏都有,MOSFET 应用电路则从十几伏到一千左右,结构如下图所示:

工作原理的区别:

对于 MOSFET 来说,仅由多子承担的电荷运输没有任何存储效应,所以很容易实现极端的开关时间。PowerMosfet 的开关的高频特性十分优秀,所以可以用在高频场和,在低电压工作状态下,开关管动作损耗远低于其他组件,但是缺点是在高压状态下,压降高,并且随着电压等级的增大,导通电阻也变大。因而其传导损耗比较大,尤其是在高电压应用场合。IGBT 是其耐压比较高,压降低,功率可以达到 5000w,IGBT 开关频率在 40-50k 之前,开关损耗也比较高,并且会出现擎柱效应。

驱动电路的对比:

驱动电路两种其实差的不是很多,只是 IGBT 输入电容要比 MOS 大,因此需要更大电压驱动功率。总之,MOS 一般在高频且低压的场合应用(即功率 < 1000W 及开关频率 > 100kHZ), 而 IGBT 在低频率高功率的场合表现较好。

二.BJT 与 MOSFET 的区别

-

三极管是电流型器件,MOSFET 是电压型器件。

-

三极管功耗大(极大的限制了三极管在集成电路中的应用),场效应管功耗小(集成电路中广泛应用)。

-

场效应管栅极基本不取电流,而三极管的基极总要吸取一定的电流。因此场效应管的输入电阻要比三极管的输入电 阻要高。

-

三极管导通电阻大,场效应管导通电阻小,只有几百毫欧,在现在的用电器件上,一般用场效应管用作开关,效率 还算比较高的。

-

场效应管的噪声系数都很小的,在低噪声放大电路的输入级及要求信噪比高的电路中要选择场效应管。

-

三极管是双极性的(内部导电方式:空穴和载流子),场效应管是单极性的(空穴 or 载流子)。

应用场合:三极管比较便宜,用起来比较方便,常用在数字电路中。MOS 常用于高速高频电路、大电流场合,以及对基极和漏极控制电流比较敏感的场合,一般来说,成本场合,普通应用先采用三极管,不行的话再 使用 MOS 管。

总之在使用场合中,BJT 的成本是最低的,MOSFET 适用于高速高频的场合,IGBT 适用的场合为高压大电流场合。

via:

-

BJT 与 MOSFET 与 IGBT 的区别_mos 和 bjt 的优缺点 - CSDN 博客

https://blog.csdn.net/pofenglangguayunfan/article/details/73229017

为什么NMOS管比PMOS管用得多–电子迁移率-宽禁带-半导体材料参数介绍

硬件工程师炼成之路 于 2021-03-16 20:43:43 发布

半导体参数,可以让我们明白当前各种半导体材料的优势与劣势的原因。

不仅如此,还可以让我们明白一些东西,特别是二极管和三极管的一些特性。

其实这些问题,如果明白了下面参数的含义,那么也就理解得差不多了。

禁带宽度

首先来看禁带宽度,这个参数是从能带模型里面来的。

固体中电子的能量是不可以连续取值的,而是一些不连续的能带,要导电就要有自由电子或者空穴存在,自由电子存在的能带称为导带(能导电)。被束缚的电子要成为自由电子,就必须获得足够能量从价带跃迁到导带,这个能量的最小值就是禁带宽度。

这段文字不好理解,那我们就以硅晶体来举例吧。

硅原子最外层含有 4 个电子,硅原子与硅原子之前通过共享电子形成晶体,这个 “共享电子” 也可以叫做形成化学键。形成化学键后,电子不能自由移动,所以不能导电。

这些形成的化学键的电子的能量是各不相同的,但他们有个特点,都处于一个范围,这个范围就叫价带。

如果这些化学键的电子获得了能量,从里面跑出来了,那它就成了自由电子。电子离开的地方形成了一个空位,所以构成了空穴,这两者都是可以导电的。同样的,所有这些自由电子的能量也各不相同,但是它们都处于一个范围,这个范围就叫导带。

可以看到,这个导带和价带中间是有间隔的,这个间隔就是禁带。禁带宽度的大小实际上是反映了价电子被束缚强弱程度的一个物理量。

禁带宽度越大,价电子必须获得比较高的能量,才能从化合键里面出来成为自由电子。所以禁带宽度越大,能够因为分子热运动成为自由电子的数量越少,导电性能越差。

等等,扯了半天这个有什么用?没发现禁带宽度大有什么用?

别急,才到问题的一半,汗。。。

在这之前,我们来复习一下 PN 结,因为做晶体管必然少不了 PN 结。

我们知道,PN 结反偏是有漏电流的,这个漏电流是由少子的扩散形成的,虽然很少,但是会有。

也就是说,会有电子从中间的内建电场区经过。并且,电子会在这个区域被加速。

如果电压足够大,场强足够高,那么电子会被加速到较高的能量与原子相撞,原本在化学键里的电子会被撞出来成为自由电子。这个新产生的自由电子又受到电场力加速,去撞击其它的原子产生新的自由电子。

这样 “一生二,二生四,子子孙孙无穷尽也”,大量的自由电子产生,电流急剧增大,这也就是 “雪崩击穿”。

如果说禁带宽度比较大,价电子被束缚的比较紧,那么就不容易被撞出来了。

所以呢,禁带宽度大,能抗住的场强也就越高,耐压也就越高。同等耐压的器件,PN 结就可以做得更薄,器件也能更小,又会带来寄生电容小的好处,器件也就能在更高的频率工作。

当温度上升,电子更容易获得能量。当温度上升到一定程度的时候,会有很多化学键里面的电子获得足够的能量变成自由电子,这样就破坏了半导体的特性。

试想一下,温度上升,自己产生的载流子比掺杂产生的载流子数量还多,那掺杂也就失去了意义,晶体管的功能也就失效了。

禁带宽度越大,需要升到更高的温度才能使化学键里面的电子变成自由电子,也就是说能工作在更高的温度。

硅的禁带宽度是 1.12eV,而碳化硅是 3.26eV。所以碳化硅器件比硅器件更耐温,可以到 200℃,而硅只能到 150℃,传闻金刚石可以工作在 500℃。

第三代半导体的特点就是禁带宽度大,所以主要应用于高温,大功率器件场合。

电子 / 空穴迁移率

电子迁移率,指的是电子在电场力作用下运动快慢的物理量。

这个不好理解,我们可以这么看。

电子浓度相同的两种半导体材料,在两端施加相同的电压,那个迁移率更大的半导体材料,它里面的电子运动速度越快,单位时间通过的电子数不就越多吗?也就是说,电流越大。

这就说明了电子迁移率越高的半导体材料,电阻率越低,通过相同的电流,损耗越小。

空穴迁移率与电子迁移率一样,空穴迁移率越高,损耗越小。但是一般说来,电子的迁移率是要比空穴要高,因为空穴是电子的空位,空穴的运动,本质上是电子从一个空穴移动到另外一个空穴。

从上表可以看到,硅材料的电子迁移率要比空穴迁移率高几倍,这也是为什么 NMOS 管比 PMOS 管用得多的主要原因。

NMOS 管在导通时,形成的是 N 型导电沟道,也就是说用来导电的是电子。而 PMOS 管导通,形成的是 P 型导电沟道,用来导电的是空穴。因为电子比空穴的迁移率要高,所以,同体积大小,同掺杂的情况下,NMOS 管的损耗要比 PMOS 管小不少。

除了功耗之外,电子空穴迁移率还影响什么呢?器件的速度

这是 NMOS 管的截止频率(输入 / 输出 = 1 时的频率)

从最终的结果可以看到,截止频率与电子迁移率成正比。也就是说,电子迁移率越高,做出的 NMOS 管可以工作在更高的频率。

这个推导过程挺复杂的,我就不列了。那么有没有通俗的理解呢?

我的想法是这样的,仅供参考。

NMOS 管的工作原理,是通过控制导电沟道,以此来控制源漏电流。在栅极加上正电压 Vgs,衬底的电子会被带正电的栅极吸引,电子充斥在源端和漏端之间,形成了导电沟道,两边就可以通了。

当 Vgs 电压以高频率变化的时候,形成的导电沟道的厚薄也会变化。这个导电沟道的变化是通过电子的移动来形成的,电子移动速度越快(电子迁移率越高),那么导电沟道就能更快的响应 Vgs 的变化。所以说,电子迁移率越高,器件的工作频率越高。

同样的,PMOS 管的工作速度,应该与空穴迁移率的大小正相关。

总的来说,电子迁移率越高,晶体管的功耗越小,速度越快。

从表中看出,二代半导体 GaAs 的电子迁移率是 8500,InP 的电子迁移率是 4600,都是比 Si 的 1350 大很多。所以二代半导体的特点就是用在高频,大功率场合。

饱和电子漂移速率

在电场比较低的时候,整体电子的漂移速度与电场大小成正比。当电场大到一定值,电子整体的漂移速度不会再增加,达到饱和,这个速度就叫电子的饱和漂移速率。

这个参数像是决定了电子漂移速率的上限。

via:

-

为什么 NMOS 管比 PMOS 管用得多 – 电子迁移率 - 宽禁带 - 半导体材料参数介绍 - CSDN 博客

https://blog.csdn.net/weixin_42005993/article/details/114899677

篇外:奥科远这篇材料有点“堆”。

CMOS(集成电路的设计工艺)

奥科远电器 2024 年 10 月 18 日 00:01 山西

导读

CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体),是一种集成电路的设计工艺,可以在硅质晶圆模板上制出 NMOS(n-type MOSFET)和 PMOS(p-type MOSFET)的基本元件,由于 NMOS 与 PMOS 在物理特性上为互补性,因此被称为 CMOS。

CMOS 一般的工艺上,可用来制作电脑电器的静态随机存取内存、微控制器、微处理器与其他数字逻辑电路系统、以及除此之外比较特别的技术特性,使它可以用于光学仪器上,例如互补式金氧半图像传感装置在一些高级数码相机中变得很常见。

芯片信息

缩写辨析

在计算机领域,CMOS 常指保存计算机基本启动信息(如日期、时间、启动设置等)的芯片。有时人们会把 CMOS 和 BIOS 混称,其实 CMOS 是主板上的一块可读写的并行或串行 FLASH 芯片,是用来保存 BIOS 的硬件配置和用户对某些参数的设定。

在今日,CMOS 制造工艺也被应用于制作数码影像器材的感光元件,尤其是片幅规格较大的单反数码相机。

另外,CMOS 同时可指互补式金氧半元件及制程。

因此时至今日,虽然因为工艺原因,都叫做 CMOS,但是 CMOS 在三个应用领域,呈现出迥然不同的外观特征:

一是用于计算机信息保存,CMOS 作为可擦写芯片使用,在这个领域,用户通常不会关心 CMOS 的硬件问题,而只关心写在 CMOS 上的信息,也就是 BIOS 的设置问题,其中提到最多的就是系统故障时拿掉主板上的电池,进行 CMOS 放电操作,从而还原 BIOS 设置。

二是在数字影像领域,CMOS 作为一种低成本的感光元件技术被发展出来,市面上常见的数码产品,其感光元件主要就是 CCD 或者 CMOS,尤其是低端摄像头产品,而通常高端摄像头都是 CCD 感光元件。

三是在更加专业的集成电路设计与制造领域。

基本介绍

CMOS 是指制造大规模集成电路芯片用的一种技术或用这种技术制造出来的芯片,是电脑主板上的一块可读写的 RAM 芯片。因为可读写的特性,所以在电脑主板上用来保存 BIOS 设置完电脑硬件参数后的数据,这个芯片仅仅是用来存放数据的。

而对 BIOS 中各项参数的设定要通过专门的程序。BIOS 设置程序一般都被厂商整合在芯片中,在开机时通过特定的按键就可进入 BIOS 设置程序,方便地对系统进行设置。因此 BIOS 设置有时也被叫做 CMOS 设置。

电脑 CMOS 设置方法

如果是兼容台式电脑,并且是 Award、AMI、Phoenix 公司的 BIOS 设置程序,那么开机后按 Delete 键或小键盘上的 Del 键就可以进入 CMOS 设置界面。

如果是品牌机(包括台式电脑或笔记本电脑),如果按 Delete 不能进入 CMOS,那么就要看开机后电脑屏幕上的提示,一般是出现【Press XXX to Enter SETUP】,我们就按 “XXX” 键就可以进入 CMOS 了。笔记本触发键一般是 F2 或者 Delete 键。

如果没有如何提示,就要查看电脑的使用说明书。如果实在找不到,那么就试一试下面的这些品牌机常用的键:

“F2”,“F10”,“F12”,“Ctrl+F10”,“Ctrl+Alt+F8”,“Ctrl+Alt+Esc” 等。

进入 CMOS 设置界面

开启计算机或重新启动计算机后,在屏幕显示 “Waiting……” 时,按下 “Del” 键就可以进入 CMOS 的设置界面。要注意的是,如果按得太晚,计算机将会启动系统,这时只有重新启动计算机了。大家可在开机后立刻按住 Del 键直到进入 CMOS。进入后,你可以用方向键移动光标选择 CMOS 设置界面上的选项,然后按 Enter 进入副选单。

设置日期

我们可以通过修改 CMOS 设置来修改计算机时间。选择第一个标准 CMOS 设定(Standard CMOS Setup),按 Enter 进入标准设定界面,CMOS 中的日期的格式为 <;;星期 ><;;月份 ><;;日期 ><;;年份 >;;,除星期是由计算机根据日期来计算以外,其它的可以依次移动光标用数字键输入,如今天是 6 月 1 日,你可以将它改为 6 月 2 日。当然,你也可以用 Page Up/Page Down 来修改。

设置启动顺序

如果我们要安装新的操作系统,一般情况下须将计算机的启动顺序改为先由软盘(A)启动或光盘 (CD-ROM)启动。选择 CMOS 主界面中的第二个选项 BIOS 特性设定(BIOS Features Setup),将光标移到启动顺序项(Boot Sequence),然后用 PageUp 或 PageDown 选择修改,其中 A 表示从软盘启动,C 表示从硬盘启动,CD-ROM 表示从光盘启动,SCSI 表示从 SCSI 设备启动,启动顺序按照它的排列来决定,谁在前,就从谁最先启动。如 C:CDROM,A,表示最先从硬盘启动,如果硬盘启动不了则从光盘启动,如果硬盘和光盘都无法启动则从 A 盘启动。在 BIOS 特性设定中,还有几个重要选项:

① Quick Power On Self Test(快速开机自检),当电脑加电开机的时候,主板 BIOS 会执行一连串的检查测试,检查的是系统和周边设备。如果该项选择了 Enabled,则 BIOS 将精简自检的步骤,以加快开机的速度。

② Boot Up Floppy Seek(开机软驱检查),当电脑加电开机时,BIOS 会检查软驱是否存在。选择 Enabled 时,如果 BIOS 不能检查到软驱,则会提示软驱错误。选择 Disabled,BIOS 将会跳过这项测试。

③ Boot UP NumLock Status(启动数字键状态),一般情况下,小键盘(键盘右部)是作为数字键用的(默认为 ON,启用小键盘为数字键),如果有特殊需要,只要将 ON 改成 OFF,小键盘就变为方向键。

④ Security Option(安全选择)

有两个选项,如果设置为 Setup 时,开机时不需要密码,进入 CMOS 时就需要密码(当然事先要设置密码)了,但只有超级用户的密码才能对 CMOS 的各种参数进行更改,普通用户的密码不行。如果设为 System 时,则开机时就需要密码(超级用户与普通用户密码都可以),到 CMOS 修改时,也只有超级用户的密码才有修改权。

设置 CPU

CPU 作为电脑的核心,在 CMOS 中有专项的设置。在主界面中用方向键移动到 “<<<CPU PLUG & PLAY>>>;;”,此时我们就可以设置 CPU 的各种参数了。在 “Adjust CPU Voltage” 中,设置 CPU 的核心电压。如果要更改此值,用方向键移动到该项目,再用 “Page UP/Page Down” 或 “+/-” 来选择合适的核心电压。然后用方向键移到 “CPU Speed”,再用 “Page UP/Page Down” 或 “+/-” 来选择适用的倍频与外频。注意,如果没有特殊需要,初学者最好不要随便更改 CPU 相关选项!。

设置密码

CMOS 中为用户提供了两种密码设置,即超级用户 / 普通用户口令设定(SUPERⅥSOR/USER PASSWORD)。口令设定方式如下:

1.选择主界面中的 “SUPERⅥSOR PASSWORD”,按下 Enter 键后,出现:Enter Password:(输入口令),

2.你输入的口令不能超过 8 个字符,屏幕不会显示输入的口令,输入完成按 Enter 键,

3.这时出现让你确认口令:“Confirm Password”(确认口令),输入你刚才输入的口令以确认,然后按 Enter 键,就设置好了。

普通用户口令与其设置一样,就不再多说了。如果您需要删除您先前设定的口令,只需选择此口令然后按 Enter 键即可(不要输入任何字符),这样你将删除你先前的所设的口令了。超级用户与普通用户的密码的区别在于进入 CMOS 时,输入超级用户的密码可以对 CMOS 所有选项进行修改,而普通用户只能更改普通用户密码,而不能修改 CMOS 中的其它参数,联系在于当安全选择(Security Option)设置为 SYSTEM 时,输入它们中任一个都可以开机。

设置硬盘参数

如果你要更换硬盘,安装好硬盘后,你要在 CMOS 中对硬盘参数进行设置。CMOS 中有自动检测硬盘参数的选项。在主界面中选择 “IDE HDD AUTO DETECTION” 选项,然后按 Enter 键,CMOS 将自动寻找硬盘参数并显示在屏幕上,其中 SIZE 为硬盘容量,单位是 MB;MODE 为硬盘参数,第 1 种为 NORMAL,第 2 种为 LBA,第 3 种为 LARGE。我们在键盘上键入 “Y” 并回车确认。

接着,系统检测其余的三个 IDE 接口,如果检测到就会显示出来,你只要选择就可以了。检测以后,自动回到主界面。这时硬盘的信息会被自动写入主界面的第一个选项 —— 标准 CMOS 设定(STANDARD CMOS SETUP)中。

保存设置

我们所做的修改工作都要保存才能生效,要不然就会前功尽弃。设置完成后,按 ESC 返回主界面,将光标移动到 “SAVE & EⅪT SETUP”(存储并结束设定)来保存(或按 F10 键),按 Enter 后,选择 “Y”,就 OK 了。

参数设置

如果 CMOS 不提供关闭操作,可使用软件设置,方法如下:

-

使用开始菜单 - 运行命令,输入 msconfig 指令;

-

选中 “BOOT.INI” 标签,进入 BOOT.INI 设置界面;

-

选择 “高级选项”,弹出高级选项设置对话框。

设置内容

大致都包含如下可设置的内容:

⒈Standard CMOS Setup:标准参数设置,包括日期,时间和软、硬盘参数等。

⒉BIOS Features Setup:设置一些系统选项。

⒊Chipset Features Setup:主板芯片参数设置。

⒋Power Management Setup:电源管理设置。

⒌PnP/PCI Configuration Setup:即插即用及 PCI 插件参数设置。

⒍Integrated Peripherals:整合外设的设置。

⒎其他:硬盘自动检测,系统口令,加载缺省设置,退出等。

电池放电

打开电脑的主机箱,可以在主板右侧看到一块 “圆” 形成扁体的电池,这块钮扣电池也称 CMOS 电池,保存主板信息的 BIOS 设置,我在网吧工作,经常碰到主机启动不了的情况,一般比较容易见效的方法是:将主机电源拔出来,意思是把电源线从电源盒拿下来,这样是完全断电状态,取下主板上的纽扣电池可以看到两个金属片,成上下,也就是正 \ 负极电路,将其对接让它短路,按着几秒钟,放电基本成功.

还有一种叫小 COMS 放电:同样将电源线从电源盒上拔下来,在这样的状态下按 “开机” 按钮,重试几下,系统也将小放电,一般也可以解决电脑无法开机的问题.

常常听到计算机高手或者非高手说 “口令忘啦?给 CMOS 放电吧。”,这到底是什么意思呢?

如果你在计算机中设置了进入口令,而你又碰巧忘记了这个口令,你将无法进入计算机。不过还好,口令是存储在 CMOS 中的,而 CMOS 必须有电才能保持其中的数据。所以,我们可以通过对 CMOS 的放电操作使计算机 “放弃” 对口令的要求。具体操作如下:

打开机箱,找到主板上的钮扣电池,将其与主板的连接断开(就是取下纽扣电池或是调整跳线),此时 CMOS 将因断电而失去内部储存的一切信息。再将钮扣电池接通,合上机箱开机,由于 CMOS 已是一片空白,它将不再要求你输入密码,此时进入 BIOS 设置程序,选择主菜单中的 “LOADBIOSDEFAULT”(装入 BIOS 缺省值)或 “LOADSETUPDEFAULT”(装入设置程序缺省值)即可,前者以最安全的方式启动计算机,后者能使你的计算机发挥出较高的性能。

数据恢复

文件 CMOS.DAT 的内容可以在 DEBUG(或 PCTOOLS 等工具软件)中显示和编辑,也可将其再写回 CMOS,这里给出自动写回数据的程序:

/*把A盘CMOS.DAT文件的数据写回CMOS中*/

#include"stdio.h"

main()

{

charcmos;FILE*fp;inti;

fp=fopen("A:\CMOS.DAT","rb");

fread(&cmos,1,64,fp);

for(i=0;i00)

命令口令

由于各种原因,有时需要破译或者摧毁 CMOS 的口令,此时可以根据具体情况采取各种不同的方法。如果能启动系统,但由于忘记或不知 CMOS 口令而无法进入 CMOS 设置状态,此时可采用程序法来破译 CMOS 的口令,用程序摧毁 CMOS 密码的设置:

/*摧毁CMOS密码*/

#include

voidfar(*p)()=MK_FP(0xffff,0x0000);

main()

{

inti;

for(i=0x34;iDEBUG

―O7010

―O7101

―Q

另外,也可以把上述操作用 DEBUG 写成一个程序放在一个文件中,具体操作如下:

C:\>DEBUG

―A100

XXXX:0100MOVDX,70

XXXX:0103MOVAL,10

XXXX:0105OUTDX,AL

XXXX:0106MOVDX,71

XXXX:0109MOVAL,01

XXXX:010BOUTDX,AL

XXXX:010C

―RCX

CX0000

:0C

―NDELCMOS.COM

―W

Writing000Cbytes

―Q

以后,只要能用软盘启动系统,运行 DELCMOS.COM 就能取消 CMOS 的设置。

历史概述

CMOS 是主板上一块可读写的 RAM 芯片,用于保存当前系统的硬件配置信息和用户设定的某些参数。CMOS RAM 由主板上的钮扣电池供电,即使系统断电信息也不会丢失。对 CMOS 中各项参数的设定和更新可通过开机时特定的按键实现(一般是 Del 键)。进入 BIOS 设置程序可对 CMOS 进行设置。一般 CMOS 设置习惯上也被叫做 BIOS 设置。

CMOS 与 BIOS

BIOS 是主板上的一块可读写的 EPROM 或 EEPROM 芯片,里面装有系统的重要信息和设置系统参数的设置程序(BIOS Setup 程序);CMOS 是主板上的一块可读写的 RAM 芯片,里面装的是关于系统配置的具体参数,其内容可通过设置程序进行读写。CMOS RAM 芯片靠钮扣电池供电,即使系统断电后信息也不会丢失。CMOS RAM 既是 BIOS 设定系统参数的存放场所,又是 BIOS 设定系统参数的结果。

CMOS 是微机主板上的一块可读写的 RAM 芯片。CMOS RAM 芯片由系统通过一块钮扣电池供电,因此无论是在关机状态中,还是遇到系统断电情况,CMOS 信息都不会丢失。

BIOS 是一组设置硬件的电脑程序,保存在主板上的一块 EPROM 或 EEPROM 芯片中,里面装有系统的重要信息和设置系统参数的设置程序 ——BIOS Setup 程序。而 CMOS 即:Complementary Metal Oxide Semiconductor—— 互补金属氧化物半导体,是主板上的一块可读写的 RAM 芯片,用来保存当前系统的硬件配置和用户对参数的设定,其内容可通过设置程序进行读写。CMOS 芯片由主板上的钮扣电池供电,即使系统断电,参数也不会丢失。CMOS 芯片只有保存数据的功能,而对 CMOS 中各项参数的修改要通过 BIOS 的设定程序来实现。CMOS RAM 既是 BIOS 设定系统参数的存放场所,又是 BIOS 设定系统参数的结果。因此,完整的说法应该是 “通过 BIOS 设置程序对 CMOS 参数进行设置”。由于 BIOS 和 CMOS 都跟系统设置密切相关,所以在实际使用过程中造成了 BIOS 设置和 CMOS 设置的说法,其实指的都是同一回事。

所谓 BIOS,实际上就是微机的基本输入输出系统 (Basic Input-Output System),其内容集成在微机主板上的一个 ROM 芯片上,主要保存着有关微机系统最重要的基本输入输出程序,系统信息设置、开机上电自检程序和系统启动自检程序等。

BIOS 功能主要包括以下方面:

一是 BIOS 中断服务程序,即微机系统中软件与硬件之间的一个可编程接口,主要用于程序软件功能与微机硬件之间实现衔接。操作系统对软盘、硬盘、光驱、键盘、显示器等外围设备的管理,都是直接建立在 BIOS 系统中断服务程序的基础上,操作人员也可以通过访问 INT5、INT13 等中断点而直接调用 BIOS 中断服务程序。

二是 BIOS 系统设置程序,前面谈到微机部件配置记录是放在一块可读写的 CMOSRAM 芯片中的,主要保存着系统基本情况、CPU 特性、软硬盘驱动器、显示器、键盘等部件的信息。在 BIOSROM 芯片中装有 “系统设置程序”,主要用来设置 CMOSRAM 中的各项参数。这个程序在开机时按下某个特定键即可进入设置状态,并提供了良好的界面供操作人员使用。事实上,这个设置 CMOS 参数的过程,习惯上也称为 “BIOS 设置”。

三是 POST 上电自检程序,微机按通电源后,系统首先由 POST (PowerOnSelfTest,上电自检)程序来对内部各个设备进行检查。通常完整的 POST 自检将包括对 CPU、640K 基本内存、1M 以上的扩展内存、ROM、主板、CMOS 存贮器、串并口、显示卡、软硬盘子系统及键盘进行测试,一旦在自检中发现问题,系统将给出提示信息或鸣笛警告。

第四为 BIOS 系统启动自举程序,系统在完成 POST 自检后,ROMBIOS 就首先按照系统 CMOS 设置中保存的启动顺序搜寻软硬盘驱动器及 CD—ROM、网络服务器等有效地启动驱动器,读入操作系统引导记录,然后将系统控制权交给引导记录,并由引导记录来完成系统的顺利启动。

相机领域

CMOS 制造工艺也被应用于制作数码影像器材的感光元件(常见的有 CCD 和 CMOS),尤其是片幅规格较大的单反数码相机。再透过芯片上的模 - 数转换器(ADC)将获得的影像讯号转变为数字信号输出。

成像过程

CCD 与 CMOS 图像传感器光电转换的原理相同,他们最主要的差别在于信号的读出过程不同;由于 CCD 仅有一个(或少数几个)输出节点统一读出,其信号输出的一致性非常好;而 CMOS 芯片中,每个像素都有各自的信号放大器,各自进行电荷 - 电压的转换,其信号输出的一致性较差。但是 CCD 为了读出整幅图像信号,要求输出放大器的信号带宽较宽,而在 CMOS 芯片中,每个像元中的放大器的带宽要求较低,大大降低了芯片的功耗,这就是 CMOS 芯片功耗比 CCD 要低的主要原因。尽管降低了功耗,但是数以百万的放大器的不一致性却带来了更高的固定噪声,这又是 CMOS 相对 CCD 的固有劣势。

集成性能

从制造工艺的角度看,CCD 中电路和器件是集成在半导体单晶材料上,工艺较复杂,世界上只有少数几家厂商能够生产 CCD 晶元,如 DALSA、SONY、松下等。CCD 仅能输出模拟电信号,需要后续的地址译码器、模拟转换器、图像信号处理器处理,并且还需要提供三组不同电压的电源同步时钟控制电路,集成度非常低。而 CMOS 是集成在被称作金属氧化物的半导体材料上,这种工艺与生产数以万计的计算机芯片和存储设备等半导体集成电路的工艺相同,因此生产 CMOS 的成本相对 CCD 低很多。同时 CMOS 芯片能将图像信号放大器、信号读取电路、A/D 转换电路、图像信号处理器及控制器等集成到一块芯片上,只需一块芯片就可以实现相机的的所有基本功能,集成度很高,芯片级相机概念就是从这产生的。随着 CMOS 成像技术的不断发展,有越来越多的公司可以提供高品质的 CMOS 成像芯片,包括:Micron、 CMOSIS、Cypress 等。

速度

CCD 采用逐个光敏输出,只能按照规定的程序输出,速度较慢。CMOS 有多个电荷 — 电压转换器和行列开关控制,读出速度快很多,大部分 500fps 以上的高速相机都是 CMOS 相机。此外 CMOS 的地址选通开关可以随机采样,实现子窗口输出,在仅输出子窗口图像时可以获得更高的速度。

噪点

CCD 技术发展较早,比较成熟,采用 PN 结或二氧化硅(SiO2)隔离层隔离噪声,成像质量相对 CMOS 光电传感器有一定优势。由于 CMOS 图像传感器集成度高,各元件、电路之间距离很近,干扰比较严重,噪点对图像质量影响很大。随着 CMOS 电路消噪技术的不断发展,为生产高密度优质的 CMOS 图像传感器提供了良好的条件。

集成电路

CMOS 同时可指互补式金氧半元件及制程。在同样的功能需求下。

自 1958 年美国德克萨斯仪器公司(TI)发明集成电路(IC)后,随着硅平面技术的发展,二十世纪六十年代先后发明了双极型和 MOS 型两种重要的集成电路,它标志着由电子管和晶体管制造电子整机的时代发生了量和质的飞跃。

MOS 是:金属 - 氧化物 - 半导体(Metal-Oxide-Semiconductor)结构的晶体管简称 MOS 晶体管,有 P 型 MOS 管和 N 型 MOS 管之分。由 MOS 管构成的集成电路称为 MOS 集成电路,而由 PMOS 管和 NMOS 管共同构成的互补型 MOS 集成电路即为 CMOS-IC(Complementary MOS Integrated Circuit)。

数字集成电路按导电类型可分为双极型集成电路(主要为 TTL)和单极型集成电路(CMOS、NMOS、PMOS 等)。CMOS 电路的单门静态功耗在毫微瓦(nw)数量级。

电路原理

采用 CMOS 技术可以将成对的金属氧化物半导体场效应晶体管(MOSFET)集成在一块硅片上。该技术通常用于生产 RAM 和交换应用系统,在计算机领域里通常指保存计算机基本启动信息(如日期、时间、启动设置等)的 RAM 芯片。

CMOS 由 PMOS 管和 NMOS 管共同构成,它的特点是低功耗。由于 CMOS 中一对 MOS 组成的门电路在瞬间要么 PMOS 导通、要么 NMOS 导通、要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。

相对于其他逻辑系列,CMOS 逻辑电路具有以下优点:

1、允许的电源电压范围宽,方便电源电路的设计

2、逻辑摆幅大,使电路抗干扰能力强

3、静态功耗低

4、隔离栅结构使 CMOS 器件的输入电阻极大,从而使 CMOS 期间驱动同类逻辑门的能力比其他系列强得多。

发展历史

早期的 CMOS 元件和主要的竞争对手 BJT 相比,很容易受到静电放电(Electro Static Discharge,ESD)的破坏。而新一代的 CMOS 芯片多半在输出入接脚(I/O pin)和电源及接地端具备 ESD 保护电路,以避免内部电路元件的闸极或是元件中的 PN 接面(PN-Junction)被 ESD 引起的大量电流烧毁。

CMOS 由 PMOS 管和 NMOS 管共同构成,它的特点是低功耗。由于 CMOS 中一对 MOS 组成的门电路在瞬间要么 PMOS 导通、要么 NMOS 导通、要么都截止,比线性的三极管 (BJT)效率要高得多,因此功耗很低,因此,计算机里一个纽扣电池就可以给它长时间地提供电力。

逻辑优点

相对于其他逻辑系列,CMOS 逻辑电路具有以下优点:

⒈ 允许的电源电压范围宽,方便电源电路的设计

⒉ 逻辑摆幅大,使电路抗干扰能力强

⒊静态功耗低

⒋ 隔离栅结构使 CMOS 期间的输入电阻极大,从而使 CMOS 期间驱动同类逻辑门的能力比其他系列强得多

CMOS 发展比 TTL 晚,但是以其较高的优越性在很多场合逐渐取代了 TTL。

以下比较两者性能,大家就知道其原因了。

⒈ CMOS 是场效应管构成,TTL 为双极晶体管构成

⒉ CMOS 的逻辑电平范围比较大(5~15V),TTL 只能在 5V 下工作

⒊ CMOS 的高低电平之间相差比较大、抗干扰性强,TTL 则相差小,抗干扰能力差

⒋ CMOS 功耗很小,TTL 功耗较大(1~5mA / 门)

⒌ CMOS 的工作频率较 TTL 略低,但是高速 CMOS 速度与 TTL 差不多相当。

详细信息

1、TTL 电平

输出高电平 > 2.4V,输出低电平 < 0.4V。在室温下,一般输出高电平是 3.5V,输出低电平是 0.2V。最小输入高电平和低电平:输入高电平 >=2.0V,输入低电平 <=0.8V,噪声容限是 0.4V。

2、CMOS 电平

1 逻辑电平电压接近于电源电压,0 逻辑电平接近于 0V。而且具有很宽的噪声容限。

3、电平转换电路

因为 TTL 和 CMOS 的高低电平的值不一样(ttl5v<==>cmos 3.3v),所以互相连接时需要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。

4、驱动门电路

OC 门,即集电极开路门电路,OD 门,即漏极开路门电路,必须外接上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。

5、TTL 和 CMOS 电路比较

1)TTL 电路是电流控制器件,而 CMOS 电路是电压控制器件。

2)TTL 电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

CMOS 电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

CMOS 电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

3)CMOS 电路的锁定效应(擎柱效应):

CMOS 电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,CMOS 的内部电流能达到 40mA 以上,很容易烧毁芯片。

防御措施:

1)在输入端和输出端加钳位电路,使输入和输出不超过规定电压。

2)芯片的电源输入端加去耦电路,防止 VDD 端出现瞬间的高压。

3)在 VDD 和外电源之间加限流电阻,即使有大的电流也不让它进去。

4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启 CMOS 电路得电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭 CMOS 电路的电源。

6,CMOS 电路的使用注意事项

1)CMOS 电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。

2)输入端接低内阻的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的

电流限制在 1mA 之内。

3)当接长信号传输线时,在 CMOS 电路端接匹配电阻。

4)当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为 R=V0/1mA.V0 是外界电容上的电压。

5)CMOS 的输入电流超过 1mA,就有可能烧坏 CMOS。

7,TTL 门电路中输入端负载特性(输入端带电阻特殊情况的处理)

1)悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。

2)在门电路输入端串联 2.5K 电阻后再输入低电平,输入端出呈现的是高电平而不是低电平。因为由 TTL 门电路的输入端负载特性可知(以 74 系列 TTL 反相器的典型电路为例),只有在输入端接的串联电阻小于 910 欧时,它输入来的低电平信号才能被门电路识别出来,串联电阻高于 2.5K 的话输入端就一直呈现高电平。这个一定要注意。CMOS 门电路就不用考虑这些了。

8,TTL 和 CMOS 电路的输出处理

TTL 电路有集电极开路 OC 门,MOS 管也有和集电极对应的漏极开路的 OD 门,它的输出就叫做开漏输出。OC 门在截止时有漏电流输出,那就是漏电流,为什么有漏电流呢?那是因为当三极管截止的时候,它的基极电流约等于 0,但是并不是真正的为 0,经过三极管的集电极的电流也就不是真正的 0,而是约 0。而这个就是漏电流。开漏输出:OC 门的输出就是开漏输出;OD 门的输出也是开漏输出。它可以吸收很大的电流,但是不能向外输出的电流。所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。OD 门一般作为输出缓冲 / 驱动器、电平转换器以及满足吸收大负载电流的需要。

9,什么叫做图腾柱,它与开漏电路有什么区别 ?

TTL 集成电路中,输出有接上拉三极管的输出叫做图腾柱输出,没有的叫做 OC 门。因为 TTL 就是一个三级关,图腾柱也就是两个三级管推挽相连。所以推挽就是图腾。一般图腾式输出,高电平 400UA,低电平 8MA**。**

制造过程

⒈p 肼 CMOS 工艺

p 肼 CMOS 工艺采用轻掺杂的 N 型衬底制备 PMOS 器件。为了做出 N 型器件,必须先在 N 型衬底上做出 P 肼,在 p 肼内制造 NMOS 器件。

典型的 P 肼硅栅 CMOS 工艺从衬底清洗到中间测试,总共 50 多道工序,需要 5 次离子注入,连同刻钝化窗口,共 10 次光刻。下面结合主要工艺流程来介绍 P 肼硅栅 CMOS 集成电路中元件的形成过程。

(1) 光 1—— 光刻肼区,刻出肼区注入孔。

(2) 肼区注入及推进,形成肼区。

(3) 去除 SiO2,长薄氧,长 Si3N4

(4) 光 2—— 反刻有源区(光刻场区),反刻出 P 管、N 管的源、漏和栅区。

(5) 光 3—— 光刻 N 管场区,刻去 N 管区上的胶,露出 N 管场区注入孔。N 管场区注入,以提高场开启,减 少闩锁效应及改善肼的接触。

(6) 长场氧化层,出去 Si3N4,再飘去薄的 SiO2,然后长栅氧化层。

(7) 光 4—— 光刻 P 管区。p 管区注入,调节 PMOS 管的开启电压,然后长多晶硅。

(8) 光 5—— 反刻多晶硅,形成多晶硅栅及多晶硅电阻。

(9) 光 6—— 光刻 P + 区,刻去 P 管及其他 P + 区上的胶。P + 区注入,形成 PMOS 管的源、漏区及 P + 保护环。

(10) 光 7—— 光刻 N + 区,刻去 N + 区上的胶。N + 区注入,形成 NMOS 管的源、漏区及 N + 保护环。

(11) 长 PSG

(12)光 8—— 光刻引线孔。可在生长磷硅玻璃后先开一次孔,然后再磷硅玻璃回流及结注入推进后再开第二次孔。

(13) 光 9—— 反刻铝引线。

(14) 光 10—— 光刻压焊块。

逻辑历史

早期分离式 CMOS 逻辑元件只有 “4000 系列” 一种(RCA ‘COS/MOS’ 制程),到了后来的 “7400 系列” 时,很多逻辑芯片已经可以利用 CMOS、NMOS,甚至是 BiCMOS(双载流子互补式金氧半)制程实现。

早期的 CMOS 元件和主要的竞争对手 BJT 相比,很容易受到静电放电(ElectroStatic Discharge, ESD)的破坏。而新一代的 CMOS 芯片多半在输出入接脚(I/O pin)和电源及接地端具备 ESD 保护电路,以避免内部电路元件的栅极或是元件中的 PN 结(PN-Junction)被 ESD 引起的大量电流烧毁。不过大多数芯片制造商仍然会特别警告使用者尽量使用防静电的措施来避免超过 ESD 保护电路能处理的能量破坏半导体元件,例如安装内存模组到个人电脑上时,通常会建议使用者配戴防静电手环之类的设备。

此外,早期的 CMOS 逻辑元件(如 4000 系列)的操作范围可由 3 伏特至 18 伏特的直流电压,所以 CMOS 元件的栅极使用铝做为材料。而多年来大多数使用 CMOS 制造的逻辑芯片也多半在 TTL 标准规格的 5 伏特底下操作,直到 1990 年后,有越来越多低功耗的需求与信号规格出现,取代了虽然有着较简单的信号接口、但是功耗与速度跟不上时代需求的 TTL。此外,随着 MOSFET 元件的尺寸越做越小,栅极氧化层的厚度越来越薄,所能承受的栅极电压也越来越低,有些最新的 CMOS 制程甚至已经出现低于 1 伏特的操作电压。这些改变不但让 CMOS 芯片更进一步降低功率消耗,也让元件的性能越来越好。

近代的 CMOS 栅极多半使用多晶硅制作。和金属栅极比起来,多晶硅的优点在于对温度的忍受范围较大,使得制造过程中,离子布值(ion implantation)后的退火(anneal)制程能更加成功。此外,更可以让在定义栅极区域时使用自我校准(self-align)的方式,这能让栅极的面积缩小,进一步降低杂散电容(stray capacitance)。2004 年后,又有一些新的研究开始使用金属栅极,不过大部分的制程还是以多晶硅栅极为主。关于栅极结构的改良,还有很多研究集中在使用不同的栅极氧化层材料来取代二氧化硅,例如使用高介电系数介电材料(high-K dielectric),目的在于降低栅极漏电流(leakage current)。

其他缩写

CMOS(Cross Media OptimizationStudy,优化研究)

美国 IAB 互动广告署 (Internet Advertising Bureau) 于 2003 年起联合知名品牌广告主、媒体、媒介代理等参与方,共同推动 XMOS 跨媒体优化研究(Cross Media Optimization Study),吸引多芬、麦当劳、福特、ING 等众多品牌参与,以及 Google,Yahoo,AOL、MSN、cnet 等媒体。

IAB 在英国、欧洲、澳大利亚等互联网广告较为成熟的国家同步推进,对于提高广告投放 ROI 形成了非常有效的指导和帮助。

调研公司 Dynamic Logic 等也在美国市场推动跨媒体研究,包含电视、互联网、平媒、户外等媒介评估 ,帮助广告主优化媒介、营销方法。

-END-

via:

-

CMOS(集成电路的设计工艺)奥科远电器 2024 年 10 月 18 日 00:01 山西

-

什么是CMOS与BIOS?又有什么区别?_bios和cmos的意思-CSDN博客 not 程序员 于 2022-03-02 14:13:05 发布

https://blog.csdn.net/weixin_45789365/article/details/123228922

-

BIOS详解:什么是BIOS ?BIOS的作用?CMOS及其与BIOS的关系? - VinoZhu - 博客园 posted @ 2016-09-16 19:38

第一篇中提到的讨论

通常所说的 CMOS 是什么意思?

xukun977

楼主 2018-8-17 17:37

相关资料

・增强的 CMOS 电荷泵和相频检测器设计

・CMOS 集成温度传感器的研究与设计.rar

・全 CMOS 三段式锂电池充电器设计

・CMOS 图像传感器的工作原理及研究

・基于 CMOS 工艺的图像传感技术研究与进展

・基于 CMOS 图像传感器的成像系统设计

・CMOS 数字成像技术在电力系统图像监控中的应用

・keys to longer life for cmos here’s how cmos can be protected against abuses

・基于 ARM 的 CMOS 数字图像传感器图像采集系统的研究与设计

xukun977 | 沙发

楼主 2018-8-17 17:40

/ CMOS 就是互补对管 /?!

咋这么有才啊?⊙∀⊙

通常所说的 CMIS 模拟集成电路设计,或 CMOS 数字集成电路设计,CMOS 指的是特定工艺,谁告你说 CMOS 就是 “对管” 的???

xukun977 | 板凳

楼主 2018-8-17 17:44

人家百度给的那个反向器,不过是 CMOS 工艺最简单实现的一个有用单元,怎么能把反向器和 CMOS 之间画等号呢?

不起眼 2018-8-18 11:42

这个楼的关键词是:互补,数字 (不连续)。大陆佬真他妈可恶,无孔不入。

不起眼 2018-8-18 11:30

人家在卖互补呢,K5 不要掺和,懂不懂啊!!!你傻啊?

king5555 + 1 平常讲 CMOS 是对应于 TTL 也就是指 4000 糸列元件,微控器手冊都有 in 丶 out 是 TTL 或 CMOS 位准。 |

xukun977 | 地板

tianxj01 | 5 楼

2018-8-18 09:06

本帖最后由 tianxj01 于 2018-8-18 09:08 编辑

xukun977 发表于 2018-8-17 17:44

CMOS 集成电路,貌似说的只是:互补金属氧化物半导体的一种制程技术,由该技术生产的芯片称为 CMOS 芯片,比如 4000 系列。

CMOS 互补对只是该技术当中的一个典型代表而已。也是构成反相器的基本单元。

真不知道什么时候,CMOS 就变成互补对了?

HWM | 6 楼

2018-8-18 09:41

tianxj01 发表于 2018-8-18 09:06

CMOS 集成电路,貌似说的只是:互补金属氧化物半导体的一种制程技术,由该技术生产的芯片称为 CMOS 芯片,比…

“CMOS” 原本就是互补 MOS 半导体技术,“MOS 对管” 是其基本的结构形式,其有多种演变形式。由此,可得高输入阻抗和低功耗等特性。

谈制程工艺,脱离基本的功能结构毫无意义,也不可能谈出点什么东西。

啊拿大 | 7 楼

2018-8-18 10:02

cmos 当然是指半导体技术啦,要叫真说 cmos 制成上还经常搞出 bjt 来呢,说 cmos 指对管确实误导了

HWM | 8 楼

2018-8-18 10:06

啊拿大发表于 2018-8-18 10:02

cmos 当然是指半导体技术啦,要叫真说 cmos 制成上还经常搞出 bjt 来呢,说 cmos 指对管确实误导了…

“CMOS” 怎么就搞出了 “BJT” 了呢?

雪山飞狐 D | 9 楼

2018-8-18 10:07

xukun977 发表于 2018-8-17 17:40

又闹笑话了,呵呵

啊拿大 | 10 楼

2018-8-18 10:14

HWM 发表于 2018-8-18 10:06

正常啊,比如 cmos 的某种 bandgap 电压参考电路,搞个 well bjt 神马的 ic 设计里常见吧

xukun977 | 11 楼

楼主 2018-8-18 10:17

人家说的是对的!

你球都不懂,在论坛装什么大师啊?

忽悠新手也就算了,碰到我是专门学集成电路设计的还想忽悠,真是胆肥啊!

xukun977 | 13 楼

楼主 2018-8-18 10:22

本帖最后由 xukun977 于 2018-8-18 10:24 编辑

啊拿大 发表于 2018-8-18 10:14

正常啊,比如 cmos 的某种 bandgap 电压参考电路,搞个 well bjt 神马的 ic 设计里常见吧…

大师正在百度或翻书呢,一书就会狡辩,说他的说法和你的说法不矛盾了。

大师,CMOS 基准中,你看见 BJT 了吗?

HWM | 14 楼

2018-8-18 10:23

啊拿大 发表于 2018-8-18 10:14

先不谈其它的,你的目的是什么?那是 “CMOS” 要的功能吗?

我多次强调,模拟电路必须以功能为先,这包括集成电路及其制程工艺。

king5555 + 1 凭大师的学识应采用谷歌,你看 x 大从不百度。我也以谷歌以准。

xukun977 | 15 楼

楼主 2018-8-18 10:40

HWM 发表于 2018-8-18 10:23

我多次强调,模拟电路必须以功能为先,这包括…

还功能为先??你以为半导体行业全要干模拟电路设计啊???

CMOS 工艺是为数字电路量身定做的,可以没考虑模拟电路设计要求,所以 CMOS 模拟电路设计是在夹缝中生存的,是在用 “数字电路” 元件来设计 “模拟电路”,所以最初的 CMOS 模拟电路性能非常差,但是比双极性便宜,性价比高,还是存活过来了,尤其是数模混合设计是主流的今天。

Lgz2006 | 16 楼

2018-8-18 10:49

只知道它是一种硅电路工艺。

雪山飞狐 D | 17 楼

2018-8-18 11:03

这么明显的错误某人还在死犟? 真是纸上谈兵,人家内行都指出你的错误了,还犟什么?有意义吗?

xukun977 | 18 楼

楼主 2018-8-18 12:22

[MOS 对管” 是其基本的结构形式,其有多种演变形式。由此,可得高输入阻抗和低功耗等特性。]

大师给家图示一下,“MOS 对管” 有多少种演变??

“MOS 管的高输入阻抗” 特性,需要演变才能有,不演变就没有啦?为何?

lihui567 | 19 楼

2018-8-18 16:08

搞集成电路设计的你俩每次都要碰一碰,

xukun977 | 20 楼

楼主 2018-8-18 17:56

本帖最后由 xukun977 于 2018-8-18 18:23 编辑

lihui567 发表于 2018-8-18 16:08

什么叫 “你俩”?人家 H 大师自报家门是搞 linux 的老师,学过本科的 C 语言设计,不过在写代码方面,这个论坛里能给他当师傅不下百人。所以大师刚来论坛还耍一耍老本行软件,后来转行自学电路了。结果是邯郸学步,电路没学会,软件也忘差不多了,最多还是 10 几年前那水平。

一路向北 lm | 21 楼

2018-8-18 22:31

互补金属氧化物半导体。

xukun977 | 22 楼

楼主 2018-8-19 13:27

这家伙果然是 “现学现卖” 的!他去翻书查资料,发现 CMOS 特有的现象 —— 闩锁效应等效电路原理图中有 BJT,于是说。。。

这家伙真是球都不懂!!!如果发生闩锁效应,电路就废了,啥都别谈了,于是一般书上都会给出 3 - 4 条避免措施。

关于这个效应的理论解释,是米国伯克利一教授提出来的,教科书上解释太粗糙了,连个动态模型都没用。

xukun977 | 23 楼

楼主 2018-8-19 13:35

最搞笑的是说话语气,什么 [这里告诉你]!这对于任何一位学过 CMOS 电路的人来说,都是常识的闩锁效应,对于他来说却是重大发现。

H 跟孔乙己一样,用手指蘸水,说你不懂茴香豆的茴字怎么写吧,我来教你,这个茴字有 4 种写法。。。

这篇孔乙己,你第一遍读想笑,第二遍读就要想哭了。大师帖子也有这个艺术效果。

tianxj01 2018-8-19 15:29

不过我还是挺喜欢这里的风格的,有那么几个人给论坛增加不少趣事和人气。

king5555 + 1 本版总是有人想出名,刚学会脚踏车就开始教人开轿车。不过的确有人会开車不会骑脚踏車。

雪山飞狐 D | 24 楼

2018-8-19 14:36

xukun977 发表于 2018-8-19 13:35

最搞笑的是说话语气,什么 [这里告诉你]!这对于任何一位学过 CMOS 电路的人来说,都是常识的闩锁效应,对于…

民科风格。。。 |

xukun977 | 25 楼

楼主 2018-8-19 15:30

前年夏天,大师能够熟练背诵运放一阶模型了,最近 2 年反复运用这个模型。

可惜画虎不成反类犬,2 年前说运用对象是运算放大器,他就只敢在运放上用,在今天的 CMOS 闩锁上就不敢用了。

如果 2 年前真的搞懂了,就不会像今天这样乱套模型了,不管什么运放电路,都要煞有介事来个一阶动态模型,搞的跟怪严谨一样。

如果 2 年前真的搞懂了,难道没发现上面的闩锁模型是不可能像课文中描述的那样,正反馈导致迅速自锁吗?该套用一阶动态模型时候,却不套了,非要画个 OP 符号才知道套?

xukun977 | 26 楼

楼主 2018-8-19 15:40

不要以为教科书上的说法就代表严谨,还有一种可能,就是简化问题,怕说复杂了读者看不懂。

下图才是闩锁等效模型,为简化模型,可以省略掉几个电阻和电容,但绝不能全删完了,尤其是 C3 电容,最好留着。

闩锁和大师说的 “晶闸管”,通常都喜用两个三极管等效,实际上使用 E - M 模型,根本不可能得到想要的结果。即大家都喜欢用,而且用了几十年的双三极管等效电路,是不对的。

122013137 | 28 楼

2018-8-20 10:35

xukun977 发表于 2018-8-18 10:22

你该拿一个纵向 NPN 的 bandgap 图来示例,要不然会说这个是寄生的 BJT,不算数

xukun977 | 29 楼

楼主 2018-8-20 11:27

122013137 发表于 2018-8-20 10:35

集成电路设计所用元件,不可能像分立元件一样丁是丁,卯是卯,电阻就是电阻,电容就是电容,集成元件里寄生虫多的很,例如一个电阻可能附赠你俩二极管,中间抽头那第三端不根据工艺接 VDD 或 GND,寄生虫导通就完蛋了。

所以说一方面 CMOS 工艺下设计模拟电路,很贫穷,没有专门的元件库,但另一方面却很灵活,究竟是什么器件,取决于你怎么用,这在分立件设计中是少见的。

如下图,究竟是 MOS 管,还是横向 BJT,看你怎么 “用” 它 =

122013137 | 30 楼

2018-8-20 14:46

xukun977 发表于 2018-8-20 11:27

集成电路设计所用元件,不可能像分立元件一样丁是丁,卯是卯,电阻就是电阻,电容就是电容,集成元件里寄…

某些标准 CMOS 工艺线,只需多一层 MASK 就可以得到一个性能优异的专用器件,甚至该工艺制程控制的好的话,不需要多出 MASK 也能提供,我上面说的纵向 NPN 就是这个意思

xukun977 | 31 楼

楼主 2018-8-20 15:10

122013137 发表于 2018-8-20 14:46

某些标准 CMOS 工艺线,只需多一层 MASK 就可以得到一个性能优异的专用器件,甚至该工艺制程控制的好的话,不…

CMOS 工艺可以制作性能优良的 BJT,下图加了个 n + 掩埋层,P 外延,n 井 =

Screenshot_2018 - 08 - 20 - 15 - 06 - 24 - 139_cn.wps.moffice_eng.png (284.53 KB, 图已挂)

xukun977 | 32 楼

楼主 2018-8-20 15:11

但是加层眼膜就要加钱啊,所以除了专业的大公司,国内一般是不让加的,老板想省钱啊!

~ eof ~