1.软件版本

matlab2013b

2.系统实现

全数字锁相环路的工作原理:环路的输入信号通常为时间上连续的信号,如单频正弦波、模拟调频信号或移频键控信号等。环路的输出信号,即数字控制振荡器的输出信号为周期性脉冲序列,其周期可调且受数字滤波器输出信号的控制。输入信号和数控振荡器的输出信号加到抽样相位检测器的输入端。在检测器中,由数控振荡器的输出脉冲序列对输入信号抽样,检测出脉冲序列与输入信号之间的相位差,并变换成数字信号作为检测器的输出信号。该信号经数字滤波器滤波后作为数控振荡器的控制信号,改变数控振荡器的周期,实现对相差的校正。

与模拟锁相环路比较,全数字锁相环路有如下特点:

(1)全部采用数字电路。由于数字电路中的有源器件工作于导通和截止两种工作状态,受干扰的影响比模拟电路小,使工作的可靠性提高。另外,数字电路易于集成化。

(2)在数字锁相环路中,时钟源通常不直接受控,不同于模拟锁相环路中的压控振荡器直接受误差信号的控制,这将有利于提高环路的性能。应用数字锁相环路,在一定范围内可以消除类似于模拟锁相环路中压控振荡器特性的非线性、环路滤波器传输函数的不稳定等的影响,从而改善锁相环路的性能。全数字锁相环已成为全数字相干通信、跟踪接收机和频率综合器中的核心部件,日益获得更广泛的应用。

系统的总体流程如下图所示:

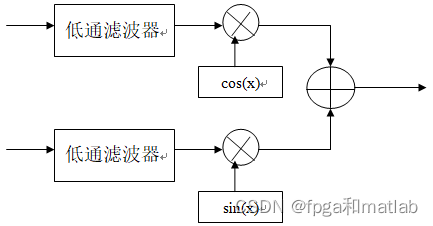

全数字锁相环的每部分都是数字的,包括数字鉴相器,数字环路滤波器,数字控制振荡器。系统发送端的基本结构:其结构如下所示:

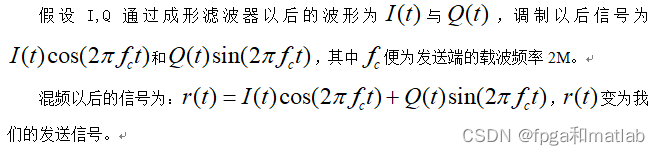

两路信号(I为上面一路,Q为下面一路)通过低通成形滤波器后与cos,sin相乘完成系统的调制,然后将两路调制信号相加完成混频,再发送出去。

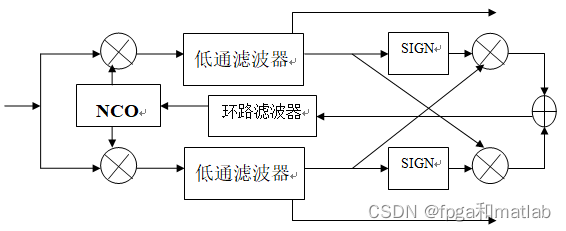

接收端的结构如下:

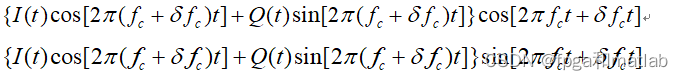

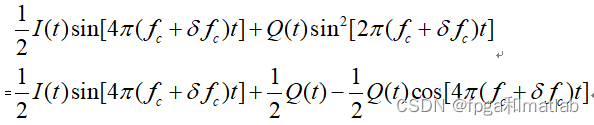

I路信号与Q路信号分别为

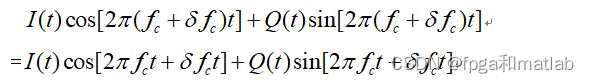

系统内部存在的频偏信号可以化解为:

解调信号为:

可以得到信号 :

3.核心程序

MATLAB代码设计说明

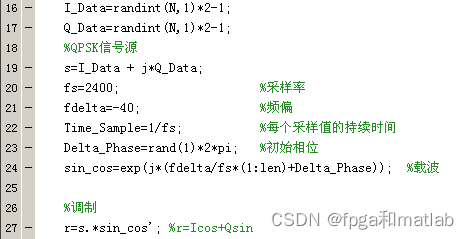

这个部分就是上面说的发送部分,即产生一个调制信号,

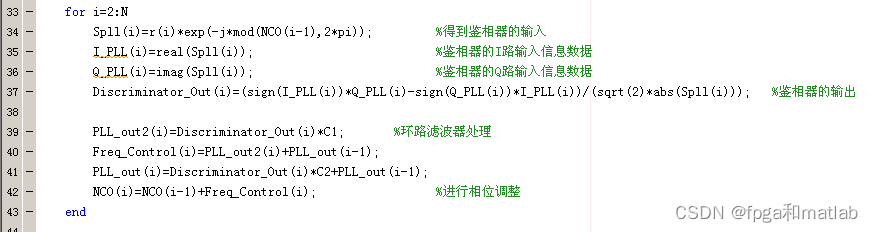

这个是锁相环部分,具体可以参考其基本结构进行对比。。。

clc;

clear;

close all;

len=1000;

N=len;

Spll=zeros(len,1); %锁相环锁定及稳定后的数据

NCO = zeros(len,1); %锁定的相位

Discriminator_Out=zeros(len,1);

Freq_Control=zeros(len,1);

PLL_out2=zeros(len,1); %锁相环频率

PLL_out=zeros(len,1); %锁相环相位

I_Data=randint(N,1)*2-1;

Q_Data=randint(N,1)*2-1;

%QPSK信号源

s=I_Data + j*Q_Data;

fs=2400; %采样率

fdelta=-40; %频偏

Time_Sample=1/fs; %每个采样值的持续时间

Delta_Phase=rand(1)*2*pi; %初始相位

sin_cos=exp(j*(fdelta/fs*(1:len)+Delta_Phase)); %载波

%调制

r=s.*sin_cos'; %r=Icos+Qsin

%环路处理

C1=0.022;

C2=0.00024;

for i=2:N

Spll(i)=r(i)*exp(-j*mod(NCO(i-1),2*pi)); %误差计算模块的输入

I_PLL(i)=real(Spll(i)); %误差计算模块的I路输入信息数据

Q_PLL(i)=imag(Spll(i)); %误差计算模块的Q路输入信息数据

Discriminator_Out(i)=(sign(I_PLL(i))*Q_PLL(i)-sign(Q_PLL(i))*I_PLL(i))/(sqrt(2)*abs(Spll(i))); %误差计算模块的输出

PLL_out2(i)=Discriminator_Out(i)*C1; %误差计算模块的输出进入环路滤波环路滤波器处理

Freq_Control(i)=PLL_out2(i)+PLL_out(i-1);

PLL_out(i)=Discriminator_Out(i)*C2+PLL_out(i-1);

NCO(i)=NCO(i-1)+Freq_Control(i); %进行相位调整

end

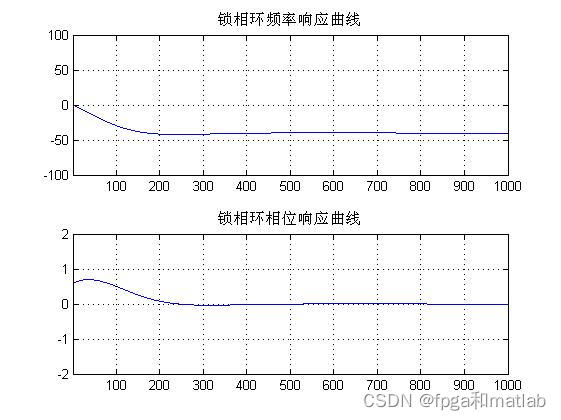

figure(1)

subplot(211)

plot(-PLL_out(2:len)*fs);

grid on;

title('锁相环频率响应曲线');

axis([1 len -100 100]);

subplot(212)

plot(PLL_out2(2:len)*180/pi);

title('锁相环相位响应曲线');

axis([1 len -2 2]);

grid on;

figure(2)

subplot(2,2,1)

plot(I_Data(500:550));

grid on;

title('I路信息数据');

axis([1,50,-2,2]);

subplot(2,2,2)

plot(Q_Data(500:550));

grid on;

title('Q路信息数据');

axis([1,50,-2,2]);

subplot(2,2,3)

plot(I_PLL(500:550));

grid on;

title('锁相环输出I路信息数据,注意可能会出现相位模糊现象,即倒PI现象');

axis([1,50,-2,2]);

subplot(2,2,4)

plot(Q_PLL(500:550));

grid on;

title('锁相环输出Q路信息数据,注意可能会出现相位模糊现象,即倒PI现象');

axis([1,50,-2,2]);

4.仿真结果

A15-01