一、实验目的

1、掌握常用组合逻辑电路的 EDA 设计方法;

2、熟练掌握基于 QuartusII 集成开发环境的组合逻辑电路设计流程;

3、加深对 VerilogHDL 语言的理解;

4、熟练掌握 DE2-115 开发板的使用方法;

5、掌握多层电路在 QuartusII 集成开发环境中的实现;

二、实验任务及要求

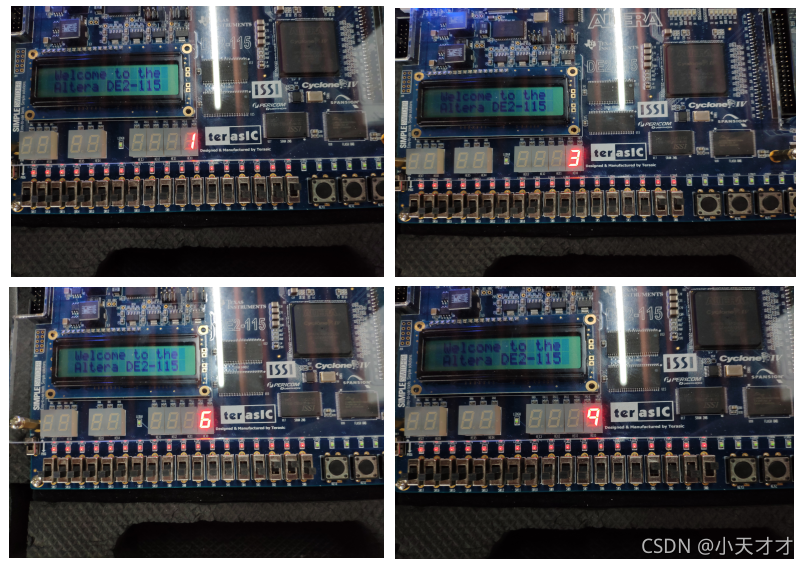

(1)任务一:4-7BCD 码译码器设计/仿真/与实现

要求:用 DE2-115 开发板上的四个拨动开关(从板子上的 18 个拨动开关中任选4个)输入BCD码,用DE2-115开发板上的一个七段数码管(从8个七段数码管中任选一个)显示译码结果。

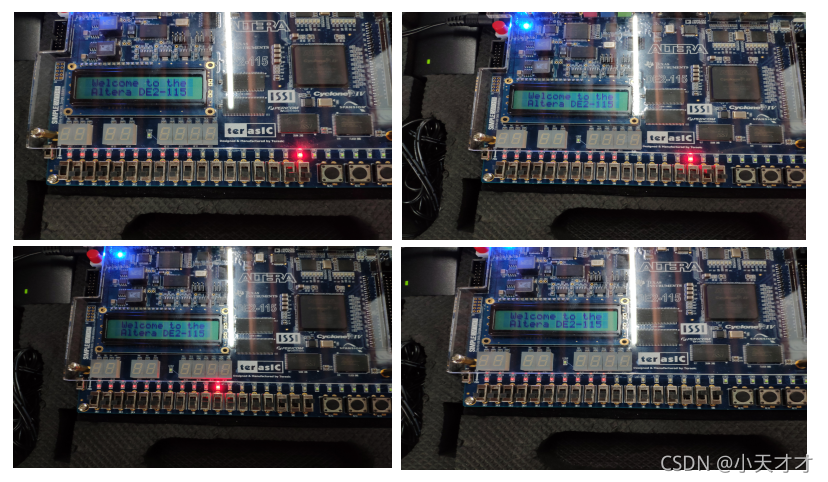

(2)任务二:3-8 译码器设计/仿真/与实现

要求:选用 DE2-115 开发板上的 3 个拨动开关(从板子上的 18 个拨动开关中任选4个)输入,选用DE2-115开发板上的8个LED灯(从 18个led红灯中任选8个)显示译码结果。

(3)任务三 :4 位全加器的设计、仿真与实现

要求:①将两个输入数据和运算结果均显示在 DE2-115 开发板的七段数码管上,用拨动开关输入数据。

②分两个模块实现:运算模块、显示模块。运算模块是主模块,调用显示模块实现输入和结果显示。

三、实验原理与步骤

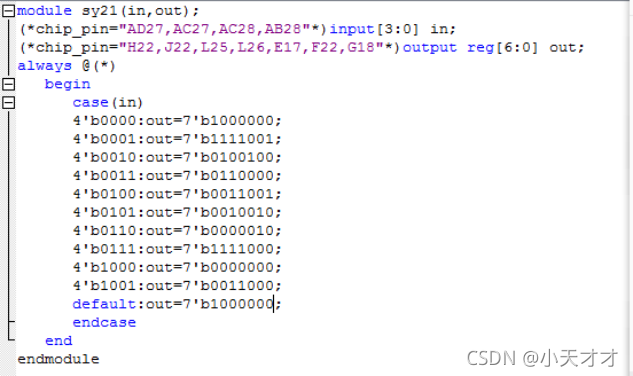

(1)任务一

①原理:通过编写verilog HDL语言来控制一个七段数码管,通过拨动开关控制灯的亮与灭。

②设计思路:通过四个拨动开关得到相应的二进制数值,再把得到的数值转换成七段数码管相应的灯所在的位置,然后使其亮或者灭。

③源程序代码:

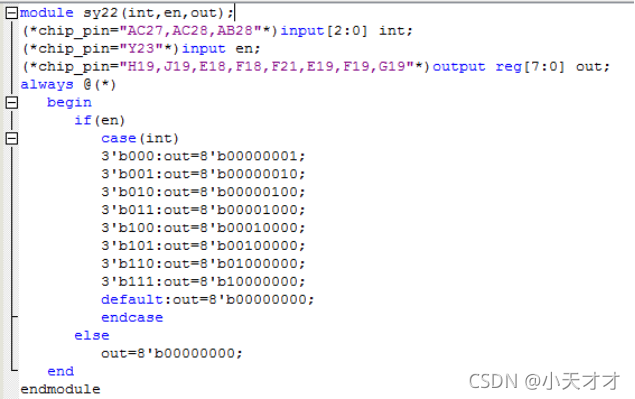

(2) 任务二

①原理:根据3-8译码器的原理来编写相应的代码,实现题目的要求,控制灯亮与灭。

②设计思路:通过三个开关输入相应的二进制数,一共有8种情况,所以分别对应着8个灯的亮与灭。

③源程序代码:

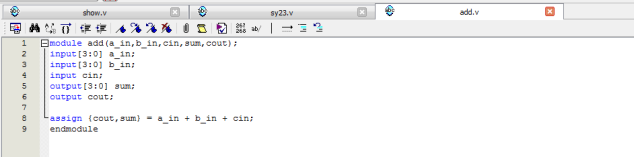

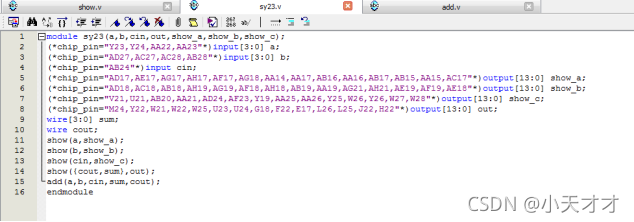

(3) 任务三

①原理:根据4位全加器的工作原理,并将其功能拆分为多个不同的模块,最终在主模块中进行调用即可实现相应的效果。

②设计思路:分为运算模块、显示模块和主模块。运算模块负责将两个二进制数相加,返回和与进位。显示模块则根据输入的二进制值将其输出为相应的BCD码。在主函数中分配好管脚,然后进行相应功能模块的调用即可。

③源程序代码:

四、实验结果与分析

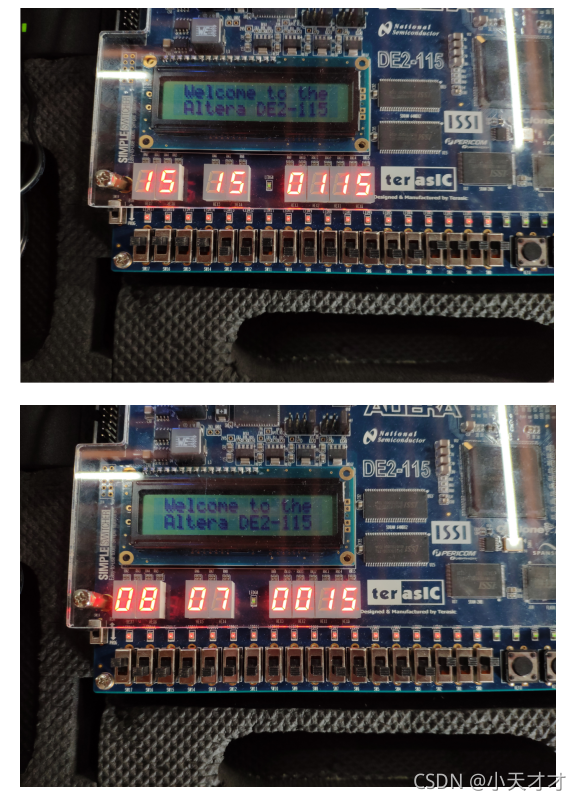

(1)任务一

(2)任务二

(3)任务三