PLL的英文全称是Phase Locked Loop,即锁相环, 是一种反馈控制电路。 PLL对时钟网络进行系统级的时钟管理和偏移控制, 具有时钟倍频、分频、相位偏移和可编程占空比的功能。对于一个简单的设计来说, FPGA整个系统使用一个时钟或者通过编写代码的方式对时钟进行分频是可以完成的, 但是对于稍微复杂一点的系统来说, 系统中往往需要使用多个时钟和时钟相位的偏移,且通过编写代码输出的时钟无法实现时钟的倍频.最后则只能通过设置锁相环实现倍频.

首先创建一个测试文件:

在Quartus II软件的菜单栏中找到【 Tools】→【 MegaWizard Plug-In Manager】按钮并点击打开

选择第一个,第一个是创建一个新的IP核,第二个是编辑一个已经创建好的IP核, 第三个是复制一个已经创建好的IP核。

自己选择路径和名称

我的晶振为50MHZ,通常我们保持默认设置, 选择In normal mode( 正常模式) 即可。然后我们直接点击【 Next>】

第一个设置是否使用异步复位来复位锁相环,第二个LOCK信号拉高表示锁相环开始稳定输出时钟信号, 在此我们保持默认的设置,直接点击【 Next>】

然后继续点击【 Next>】,一直到这个界面,Requested Setting一栏中直接输入我们需要的时钟频率100Mhz; Clock phase shift一栏中输入时钟的相位偏移,这里保持默认为0即可;Clock duty cycle( %) 一栏设置时钟的占空比,时钟占空比一般为50%, 我们在这里保持默认50即可, 然后点击【 Next>】.

在该页面中,我们使能c1时钟信号,然后将c1时钟设置为100MHz,在这里为了向大家演示设置时钟相位的作用,我们将时钟相位设置成180,然后点击【 Next>】

在该页面中,我们使能c2时钟信号,然后将c2时钟设置为50MHz,然后点击【 Next>】

在该页面中,我们使能c3时钟信号,然后将c3时钟设置为25MHz。然后点击【 Next>】

接下来都是直接点next最后finish,回到界面后点击yes

这个也就是我们生成的锁相环的引脚图:

接下来返回到工程界面,open生成的pll_clk.qip可以看到如图,表示已经生成了pllclk.v文件

接下来new一个test.v的文件

在文件中添加代码:

module test(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//输出时钟

output clk_100m , //100Mhz时钟频率

output clk_100m_180deg, //100Mhz时钟频率,相位偏移180度

output clk_50m , //50Mhz时钟频率

output clk_25m //25Mhz时钟频率

);

//wire define

wire rst_n ; //复位信号

wire locked ; //locked信号拉高,锁相环开始稳定输出时钟

//系统复位与锁相环locked相与,作为其它模块的复位信号

assign rst_n = sys_rst_n & locked;

//锁相环

pllclk u_pll_clk(

.areset (~sys_rst_n ), //锁相环高电平复位,所以复位信号取反

.inclk0 (sys_clk ),

.c0 (clk_100m ),

.c1 (clk_100m_180deg),

.c2 (clk_50m ),

.c3 (clk_25m ),

.locked (locked )

);

endmodule

然后在编译成功后目录为这样:

其中这个设置的锁相环引脚就是根据之前生成的引脚图进行的配置

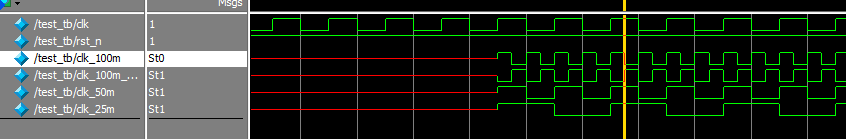

最后的仿真图如图所示:

对IP核的仿真需要在Modeslim工程中添加altera_mf文件仿真库altera\13.1\quartus\eda\sim_lib\altera_mf.v,把他复制到自己的路径下就可以了